Efinity IDE の特徴とインストール方法

これまで当ブログで紹介してきた Efinity ですが、このほど 2024.2 がリリースされましたので、これを機に特徴とインストール手順をおさらいしたいと思います。

また、Efinity 2024.2 では、新たに IO バッファや IO レジスタの推論機能が実装されたので、これらについては別の記事で紹介したいと思います。

(これまで IO トライステートバッファや IO レジスタは、Interface Designer というサブツールで設定する必要がありました)

Efinity の特徴

Efinity IDE は Windows 版と Linux 版の両方が提供されています。

Efinix Support でユーザ登録すれば誰でも無償で使うことができます。

下記に特徴を列挙します。

| 言語 | VHDL, VerilogHDL, SystemVerilog |

| タイミング制約・解析 | SDC による記述。 解析結果にグラフィカルな波形表示はなく、テキストレポートのみ。 tcl コマンドを実行することで所望のパスを解析可能。 |

| コマンドライン実行 | 可能。 seed を振るコンパイルもサポートされている。 |

| ハードマクロ | DDR3/4 や MIPI, PLL, PCIe などが有る。 ただし、HDL コードでのインスタンス化(実装) はせず、Efinity 内部のInterface Designer というサブツールでマクロの使用有無を設定する。 ハードマクロのポートをHDLトップデザインのポート宣言に追加することで、両者が接続される。 |

| デバッガ | Intel の Signal Tap II のようなロジックアナライザツール (Efinity Debugger) が有る。 Wizard 形式で観測したい信号を選び、コンパイルするだけでロジックアナライザを実装できる。 また、仮想 IO 機能 (信号を任意のタイミングで値を変更できる) も有る。仮想 IO の場合は、仮想 IO モジュールを Efinity Deubber で作成し、それをユーザロジック内にインスタンス化する。 |

| IP | MIPI, Ethernet MAC, DDR3, SDRAM, SD Host, Hyper RAM, SPI Flash, I2C, UART, SoC など。 いずれも追加ライセンス不要で使用可能。 |

| SoC | Sapphire SoC という名称で提供されている。 IP Editor で使用する Peripheral を設定すれば、自動的に CPU Core と Peripheral が接続された SoC モジュールが生成される。Perupheral としては GPIO, Timer, UART, I2C, SPI, APB3, AXI4, Custom Instruction などが有る。 CPU Core は VexRISC-V を採用している。(Intel Qsys のようにグラフィカルにバスを接続するようなツールは無い) ソフトウェアの開発環境として Eclipse ベースの "RISC-V IDE" というツールが提供されている。 ステップ実行、ウォッチ、ブレイクポイント、レジスタアクセス、メモリアクセスなどが可能。 各種 Peripheral のドライバ・サンプルコードも同梱されている。 また、Ti375 シリーズには RISC-V ハードマクロが搭載され動作周波数は 1GHz となった。 |

| シミュレーションモデル | 有り。 2024.2 からは PLL などのハードマクロ (Interface Block) のモデルも提供されるようになった。 (Efinity のインストールフォルダに有る) ただし、MIPI や DDR Controller などの高機能マクロは Efinix 社と NDA を締結することで入手可能。 |

| FPGA 書き込み | FTDI チップを経由して書き込む。 評価ボードでは FTDI チップが実装されているので USB ケーブルを接続して、ドライバをインストーすれば使える。 実際の基板設計では, ISX ケーブルや EFINIX DOWNLOAD CABLE II を使うことが多い。 |

インストール手順

ここでは Windows 版のインストール手順を紹介します。

Efinity をインストールする前に VC++ ライブラリ, Java, Zadig をインストールします。

(Efinity をインストールしたあとでも大丈夫)

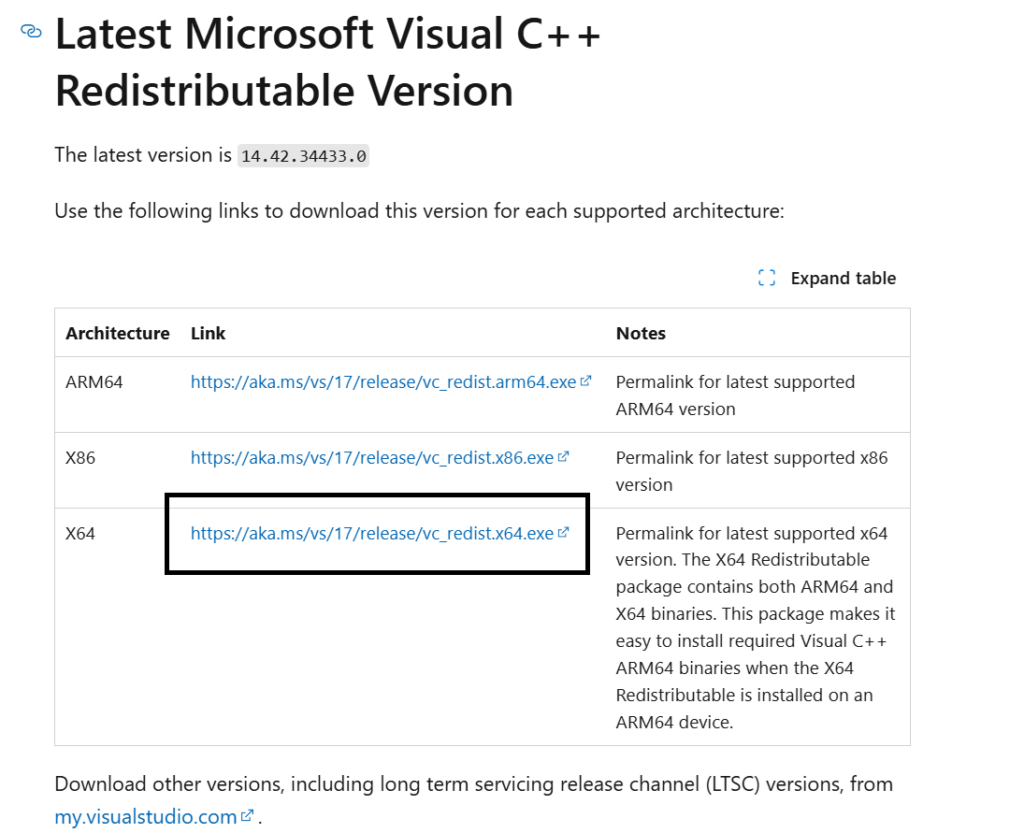

Microsoft Visual C++ 2019 x64 runtime library redistributable

Efinity Software Userguide では 2019 (or latest version) という記述があるので、最新版の X64 の exe をダウンロードしてインストールします。

https://learn.microsoft.com/en-us/cpp/windows/latest-supported-vc-redist?view=msvc-170

Java 8

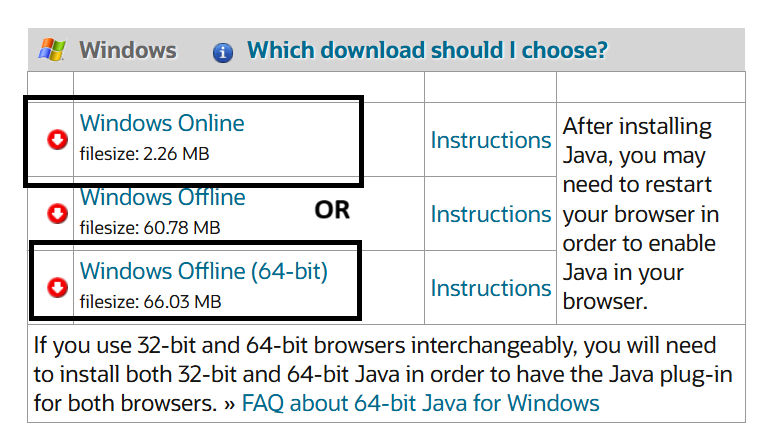

つぎに Java8 です。

Windows Online または Windows Offline (64-bit) をダウンロードしてインストールします。

Java は Efinity 内の一部ツール (IP Editor など) で使用しているようです。

https://www.java.com/en/download/manual.jsp

Zadig (ダウンロードのみ)

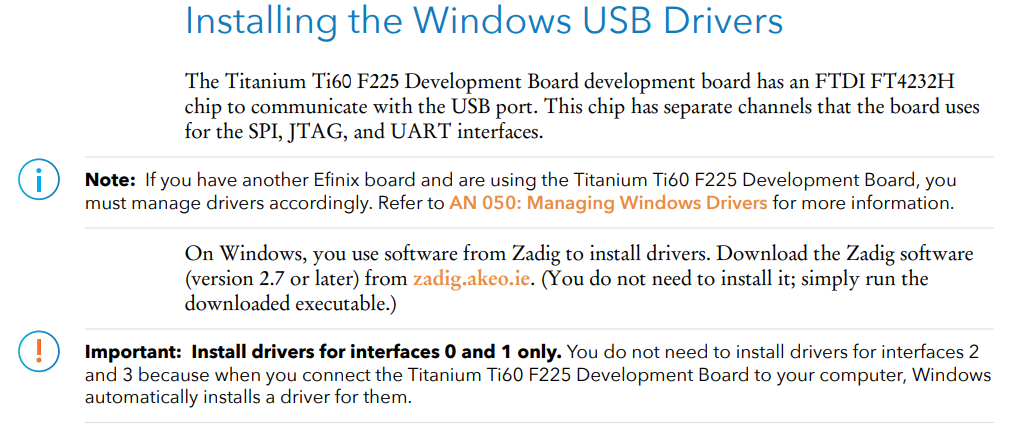

Efinity から FPGA にビットストリームを書き込む(プログラムする) ときは、FTDI チップを経由して FPGA の JTAG ポートにアクセスします。FTDI チップへのアクセスには FTDI 標準ドライバではなく libusb ドライバを使っているため、Zadig というツールをつかってドライバを書き換える必要があります。

ただし、使用中の PC から、評価ボードや FTDI チップに接続しているときでなければドライバの書き換え作業ができないので、ここでは Zadig をダウンロードするまでとします。

下記のページから Zadig 2.7 以降をダウンロードして、任意のフォルダに保存しておきます。

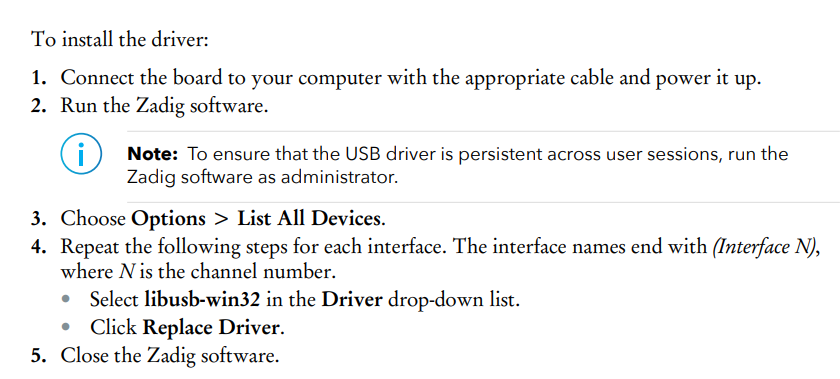

Zadig を使ったドライバの書き換え手順は、評価ボードごとに Efinix 公式サイトに掲載されていますので、そちらを参照してください。また、過去のブログ記事もあわせて参照してください。

例)

Ti60 F225 Development Kit User Guide v2.2

P5 Installing the Windows USB Drivers

Tips

この FTDI JTAG の取り扱いについて、実際に基板設計するときは下記のいずれかになるでしょう。

(1) Efinix 評価ボードの回路図を参考に FTDI チップ周りの回路を流用する。

FTDI チップのコンフィグデータ (ポートアサイン) もそのまま使う。

(2) FPGA の JTAG ポートをピンヘッダに接続する。

JTAG にアクセスするときは、Efinity がサポートしているダウンロードケーブルを使用する。

日本国内では ISX 社が開発した ISX ケーブルを使うのがメジャーなようです。

http://www.isx.co.jp/jp/recruit/isx_report/319/

他にも Digi-key やマルツパーツで販売されている EFINIX DOWNLOAD CABLE II などもあります。

Efinity 2024.2 のインストール

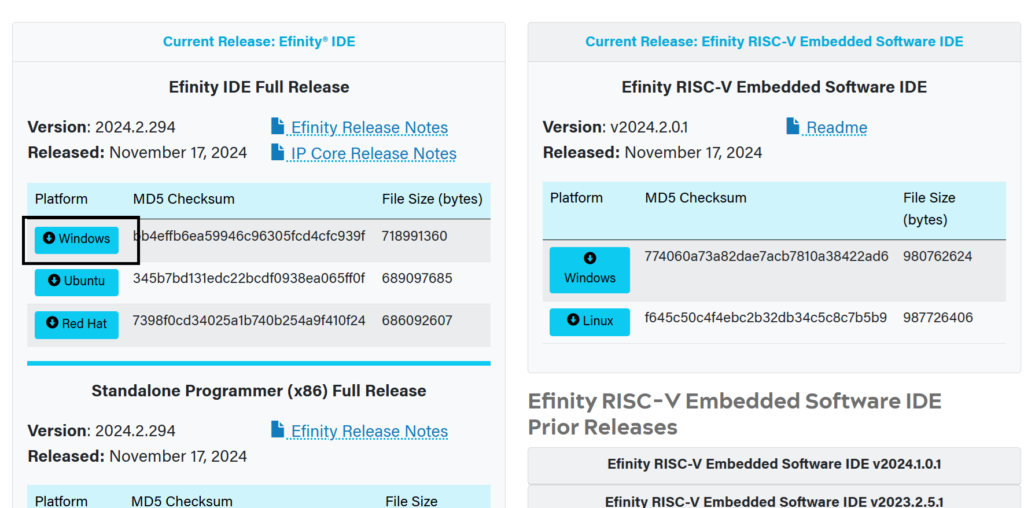

Efinity は Efinix Support にユーザ登録した後、こちらのページ からダウンロードできます。

Efinity IDE Full Release の Windows をクリックし、その後に表示される License Agreement に同意したら ( I Agree ボタン を押したら) インストーラのダウンロードが始まります。 インストーラのサイズは約 700 MB です。

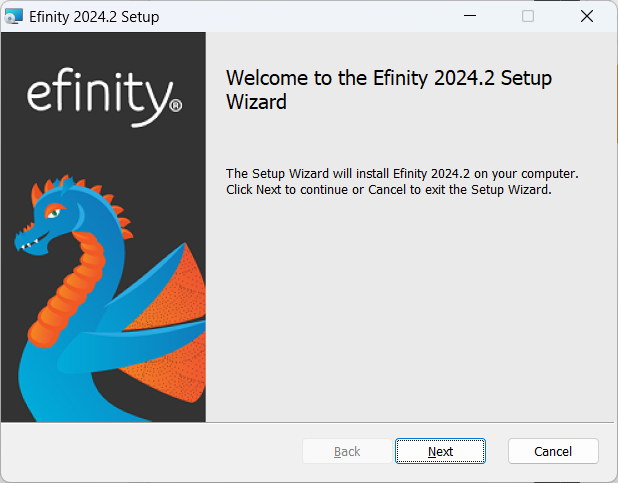

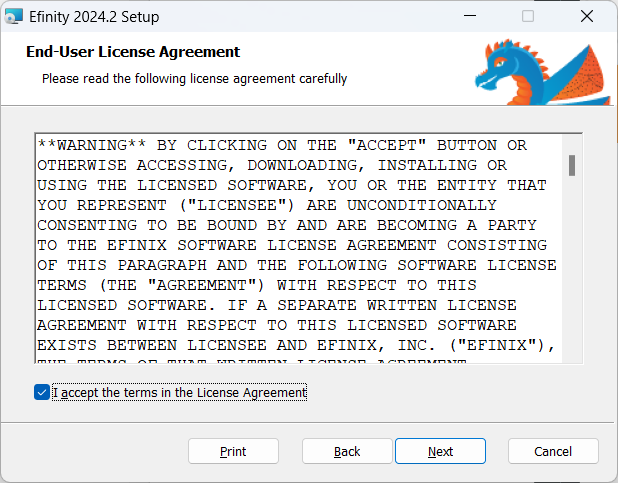

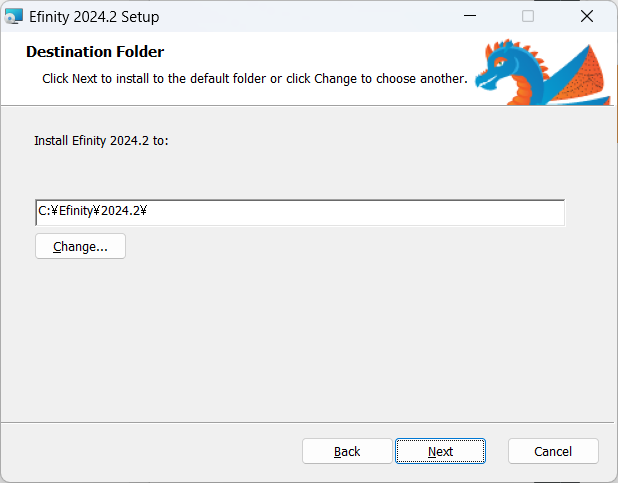

インストーラを起動したら、あとは Next と押して進むだけです。

まとめ

Efinity は後発ベンダということも有り、GUI がシンプルにまとまっている印象です。

今後、Efinity 2024.2 で新たにサポートされた機能についても書いていこうと思います。