Efinity Debugger を試す 前編 (ロジアナ編)

こんにちは!

今回は前回作成した Ti60 の L チカデザインを使って、Efinity Debugger 機能を使ってみます。

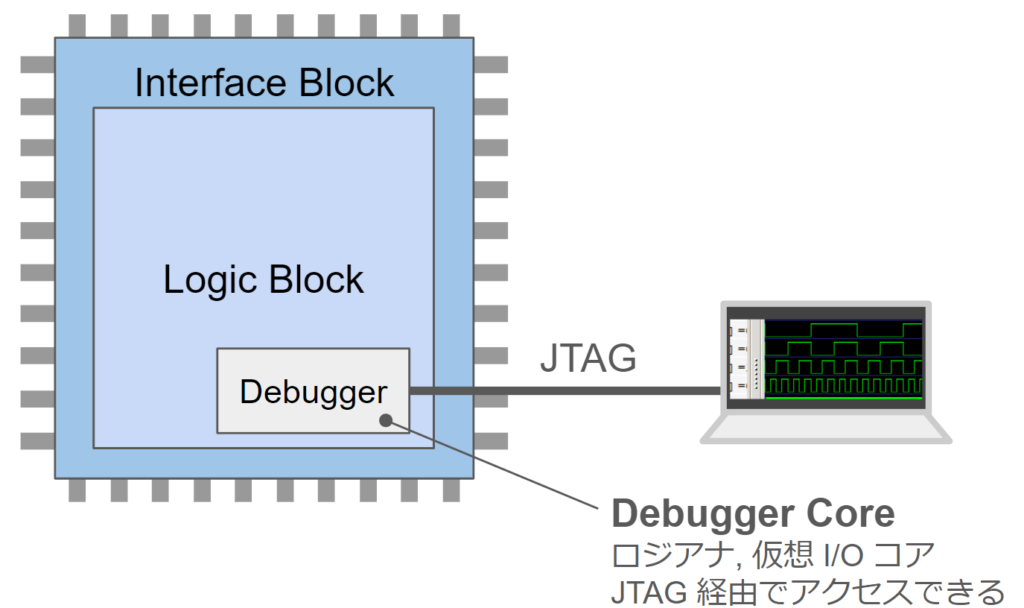

Efinity Debugger とは?

Efinity Debugger は FPGA 内部に実装できるロジアナ・仮想 IO 機能です。

AMD (Xilinx) だと Chipscope, Altera (Intel) だと SignalTap に相当する機能かと思います。

Debugger の実装方法は 2 つあります。

- 自動実装

- ロジアナ機能のみ使用できる。仮想 IO 機能は使用できない。

- ウィザード形式の GUI ツールで観測したい信号を選択し、デバッグコアを作成する。

- ソースコード (Verilog HDL, VHDL) を書き換える必要が無く、Efinity が自動的にデバッグコアを実装してくれる。

- 手動実装

- ロジアナ機能と仮想 IO 機能の両方を使える。

- ウィザード形式ではない Debugger GUI ツールでデバッグコアを作成し、ソースコードに手動で実装する。

事前準備

Efinity Debugger はロジアナ機能で取得した波形を "GTK Wave" という外部ツールで表示します。

そのため、予め PC に GTK Wave をインストールし、環境変数 PATH に GTK Wave 実行ファイルのパスを追加しておく必要があります。

GTK Wave : https://gtkwave.sourceforge.net

GTK Wave をインストール済みで、PATH も設定済みであれば、この章はスキップしてください。

GTK Wave 環境変数の設定方法

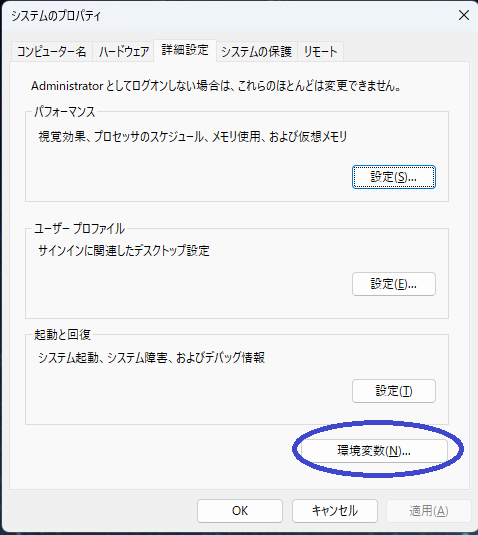

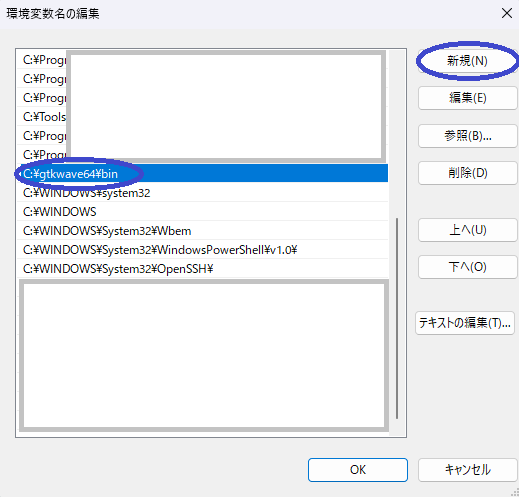

(1) Windows メニューを開き "環境変数" で検索すると、下図のように "システム環境変数の編集" が出てくるので、これを選択します。

(2) つぎに "環境変数" ボタンを押します。

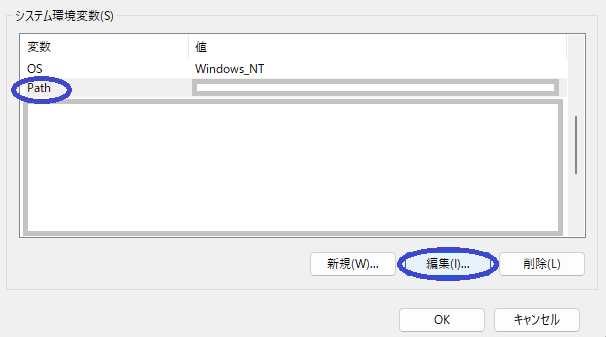

(3) システム環境変数の Path を選択して "編集" を押します。

※画像の一部を塗りつぶしています。

(4) "新規" を押して、 "C:\gtkwave64\bin" と入力します。

※GTK Wave の .exe が格納されているフォルダを入力してください。

(5) 入力したら、これまでに開いたすべてのダイアログの "OK" ボタンを押して、ダイアログを閉じていきます。

※キャンセルを押すと設定値がもとに戻ってしまうので注意してください。

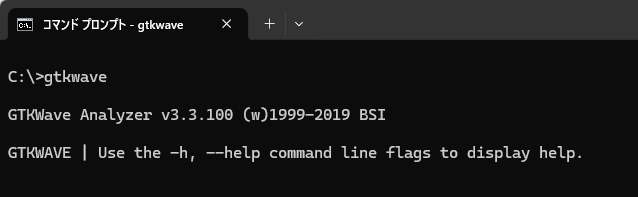

(6) 試しにコマンドプロンプトを開いて、gtkwave を実行します。

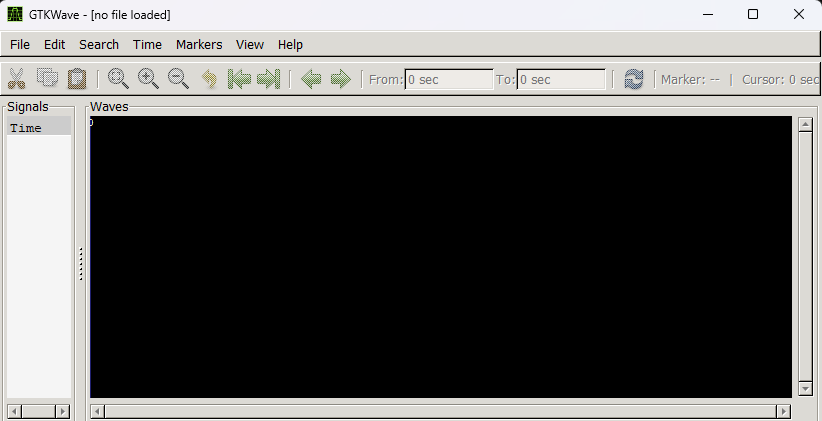

(7) GTK Wave のウインドウが表示されれば準備完了です。

自動実装 (Auto Instantiation) を試してみる

自動実装はとても簡単です。

(1) デバッグ対象のデザインを用意して Efinity で開きます。

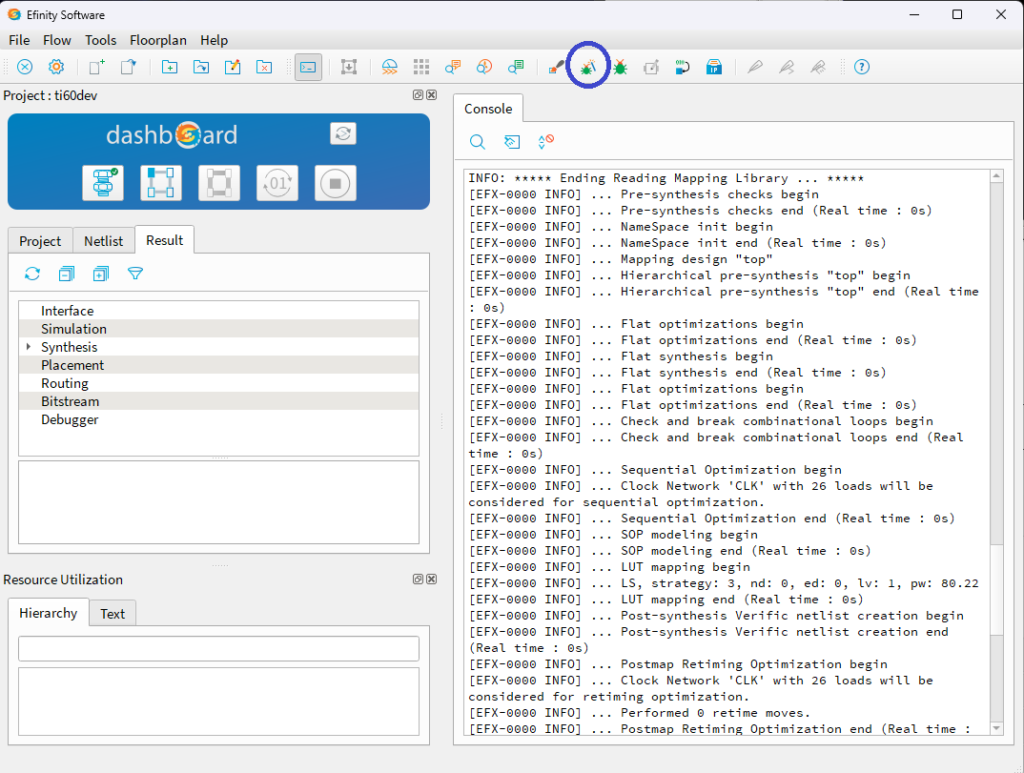

(2) Syhthesis が完了している状態で、Debugger Wizard を押します。

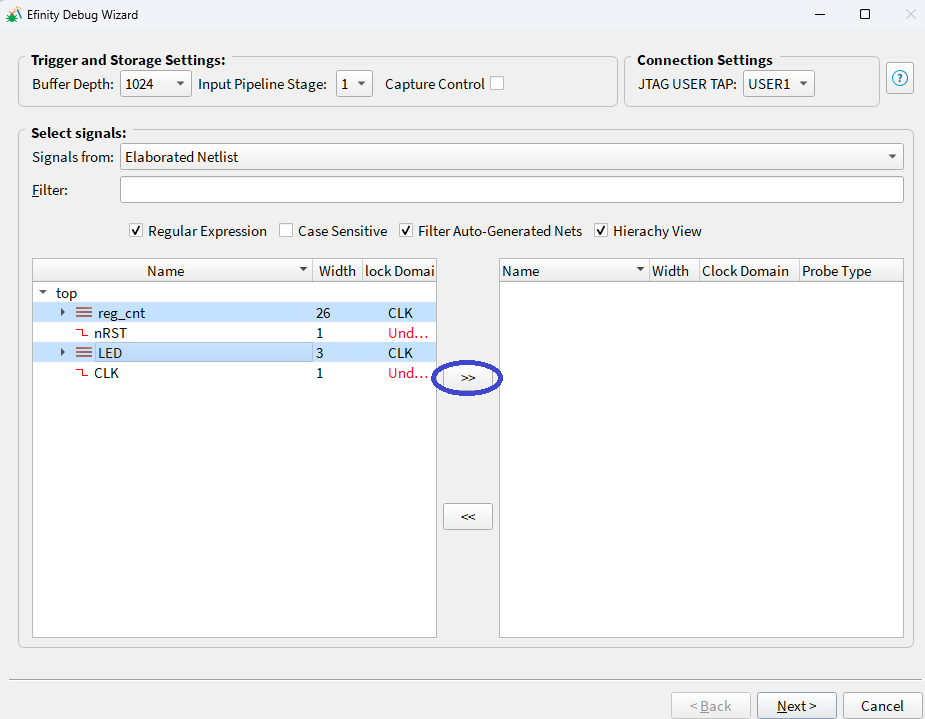

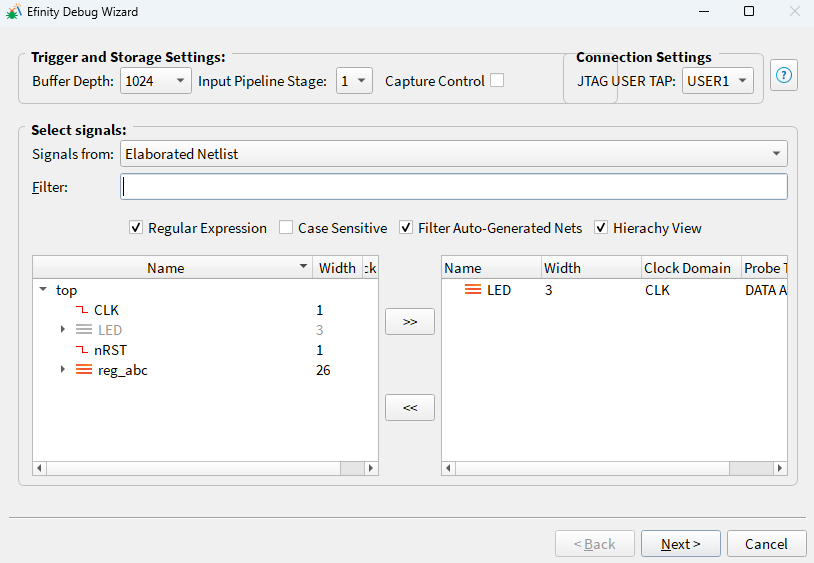

(2) 信号リストが表示されるので、観測したい信号を選択して >> ボタンを押します。

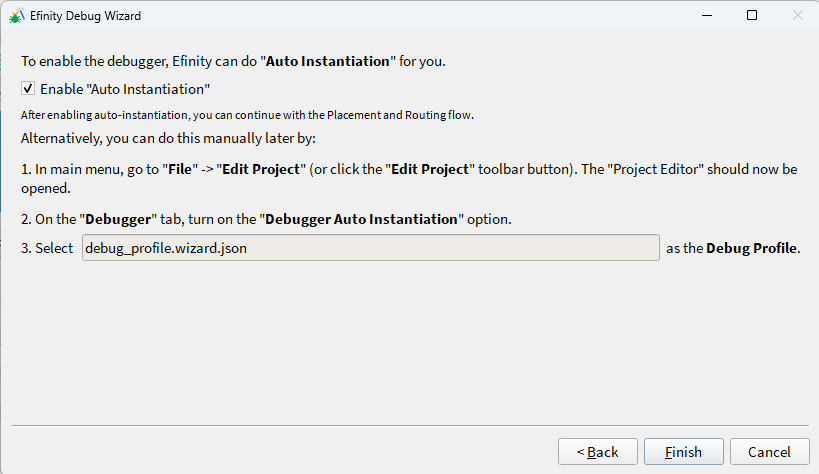

(3) "Next>" を押し、Auto Instantiation にチェックを入れて "Finish" を押します。

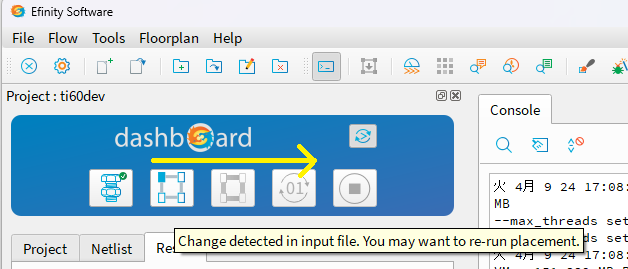

(4) あとは通常通り Placement, Routing, Generating Bitstream まで実行します。

Synthesis を再実行しても問題有りません。

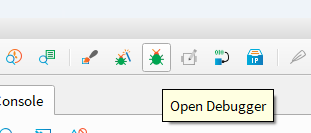

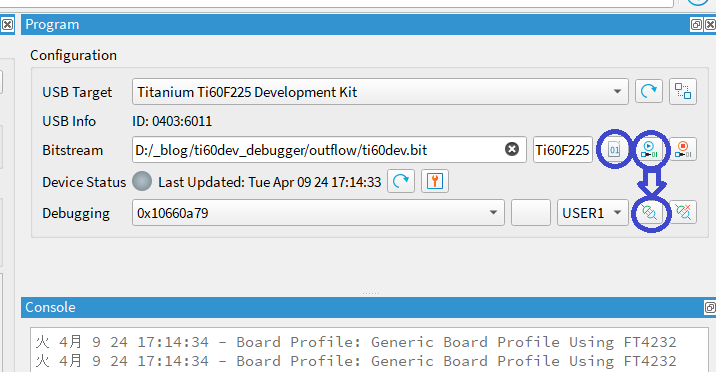

(5) Generating Bitstream まで完了したら、評価ボードの電源を ON にして Open Debugger アイコンを押します。

(6) Programming エリアで .bit ファイルを選択し、プログラムを実行します。

※Programming は Debugger ではなく、Programmer を使用しても良いです。(.bit または .hex)

プログラムが終わったら "Connect Debugger" ボタンを押します。

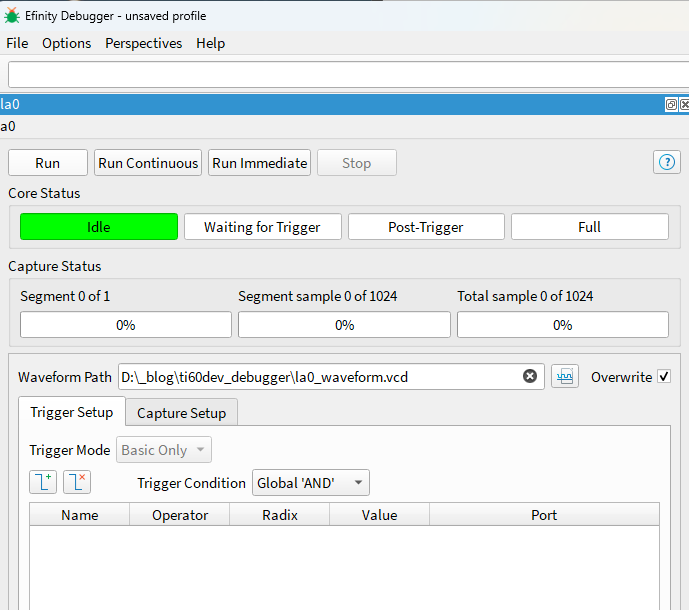

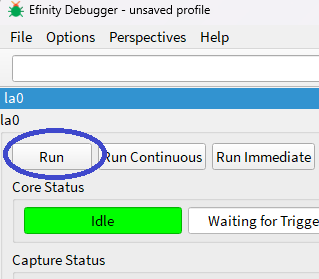

(7) Connect して緑色の "Idle" が表示されれば、Debugger へのアクセスが成功です。

(8) トリガ条件等は設定せず、この状態のまま Run Immediate を押してみて、GTK Wave で波形が表示されれば OK です。

ロジアナで出来ること

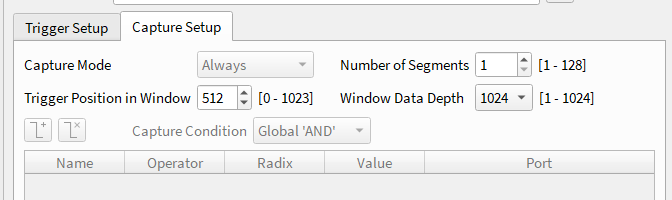

Efinity Debugger のロジアナ機能の動作として、下記のことを設定できます。

(スクショ画像を見ていただくのが早いかと思います)

これら、Debugger の Trigger Setup / Capture Setup で設定できる項目は、値を変更しても再コンパイルは不要です。

※観測対象の信号や Depth 最大値を変更する場合は再コンパイルが必要です。

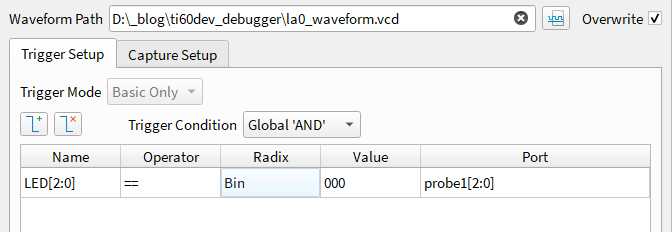

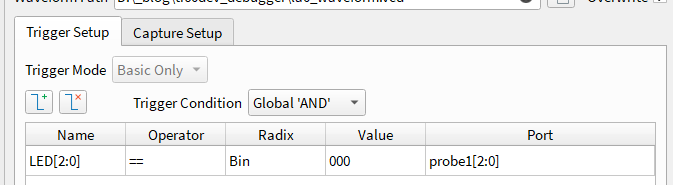

- トリガ信号の選択、トリガ条件の設定

- キャプチャ開始位置 (Tripper Position)

- キャプチャ回数 (Number of Segments)

- トリガ条件が複数回発生する場合に便利です。

- 分周クロックで動作するバスを観測するにも便利です。

- I2C の SCL を Rise で Number of Segments = 16 に設定するなど

- 波形データの深さ (Window Data Depth)

- 1 Segment の キャプチャデータの深さです。

- デバッガコアの Depth が 1024 である場合、Number of Segments を 4 に設定すると、Window Data Depth は 256 になります。(1024 / 4 = 256)

上記のトリガ条件を設定したときは "Run" ボタンで波形キャプチャをスタートさせます。

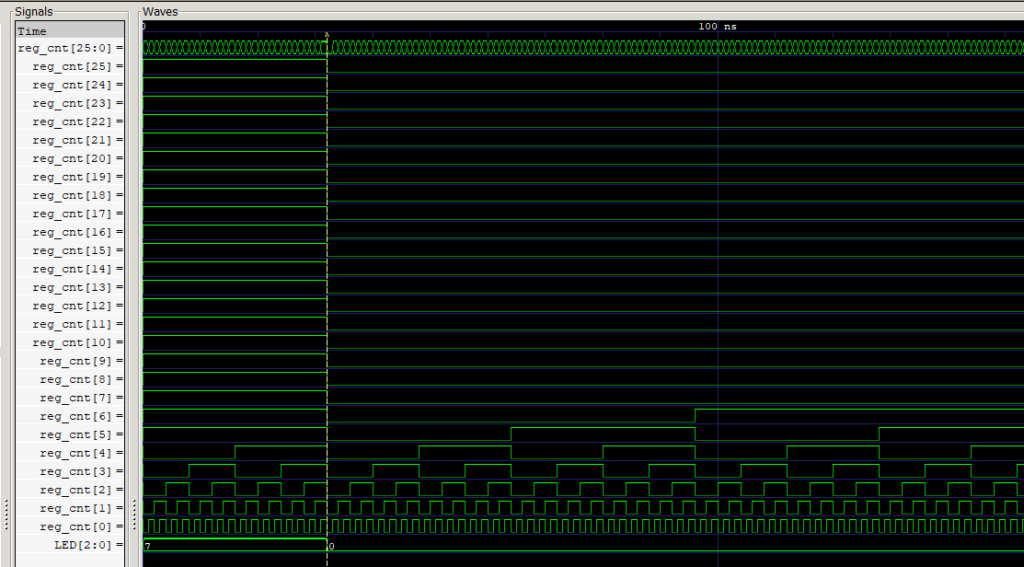

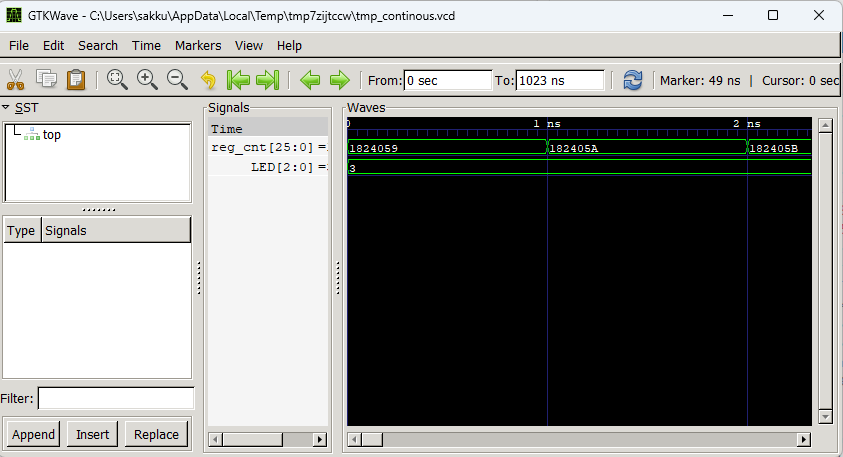

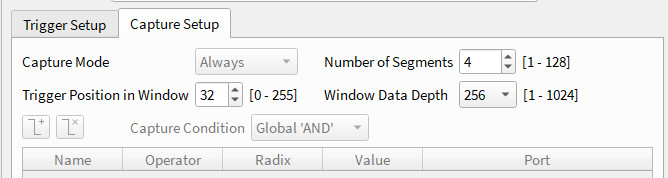

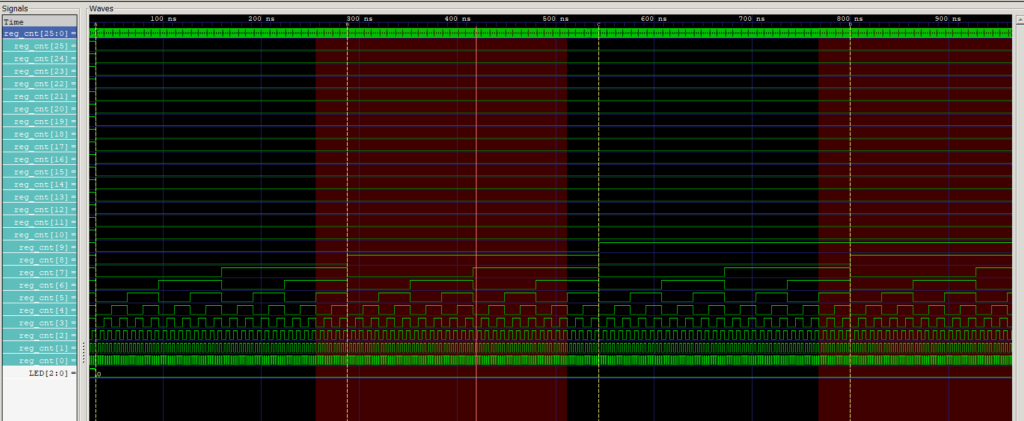

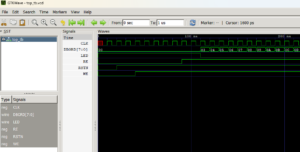

Number of Segments = 4 の実行例

試しに上記の条件で波形キャプチャを実行してみます。

Number of Segments = 4, Trigger Position in Window = 32 とします。

※1 Segment あたりのキャプチャ幅が 256 で、各 Segment の Trigger Position が 32 の位置になります。

結果、下図のように Segment 毎に色分けされて波形表示されます。

今回はカウンタをキャプチャしたので、単純な波形に鳴ってしまいました...^^;

その他 Tips

Efinity 2023.2 patch3 で連続キャプチャ機能が実装された!

Efinity 2023.2 patch2 以前は波形キャプチャの度に GTK Wave が再起動し、せっかく設定したビューがクリアされてしまいましたが、Efinity 2023.2 patch3 からは GTK Wave のウィンドウが開かれたまま波形がリロードされるようになりました。

これにともない、Efinity Debugger に Run Continuous モードが追加され便利になりました。

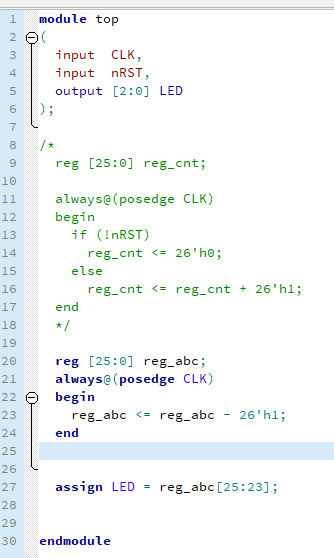

Debugger Core で観測しているネットをソースコードで削除したとき

さきほど Debugger のウィザードで選択した reg_cnt を削除して、替わりに reg_abc を追加してみます。

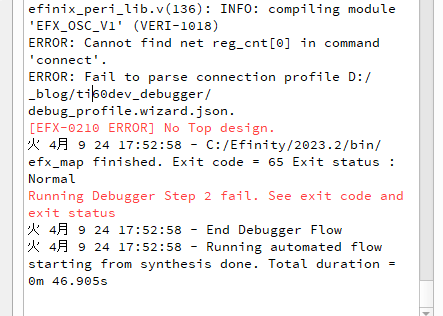

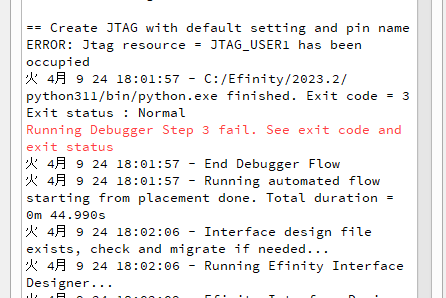

この状態でコンパイルを実行すると下記のようなエラーメッセージが表示されます。

これは Debugger で選択した信号を、Debugger に接続できなかったことを示しています。

このエラーを解消するためには、Debugger Wizard を開いて、

何も変更せずに "Next>" "Finish" を押し、Debugger Core を再生成すれば OK です。

(再生成後は再コンパイルします)

自動実装 (Auto Instantiation) を止めたいとき

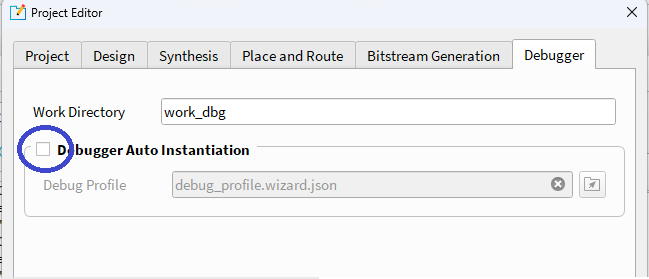

デバッグ作業が終了して、Debugger をデザインから外したいときは、下記手順で自動実装 (Auto Instantiation) を無効にします。

(1) File - Edit Project を選択します。

(2) Debugger タブの Debugger Auto Instantiation のチェックボックスを外して "OK" ボタンを押します。

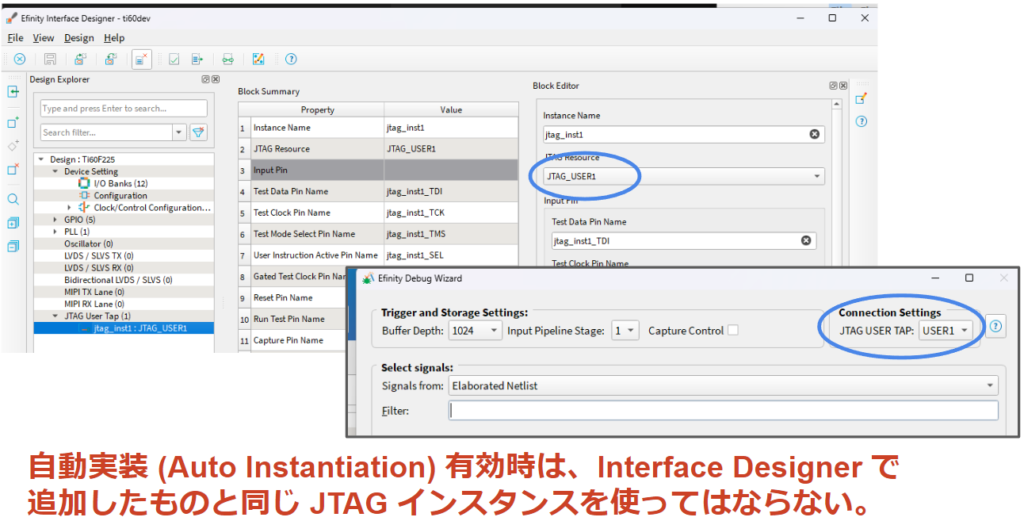

JTAG インスタンスが競合している時

今後のブログ記事でも紹介しますが、Efinix の Sapphire SoC を使う際に、Interface Designer で JTAG インスタンスを追加する必要があります。

このとき、Interface Designer で追加した JTAG インスタンスと自動実装 (Auto Instantiation) で指定した JTAG インスタンスが同じ場合、コンパイルエラーになります。

この場合、Interface Dsigner で追加した JTAG インスタンスと自動実装の JTAG インスタンスは、それぞれ別のものを選択してください。

次回

次回 (後編) は 仮想 IO を試してみます!

“Efinity Debugger を試す 前編 (ロジアナ編)” に対して2件のコメントがあります。