Efinity で ICARUS Verilog (iVerilog) シミュレータを実行

AMD や Altera の FPGA EDA ツールにはシミュレータが付属していますが、Efinix の Efinity にはシミュレータが付属していません。

替わりに、Efinix 公式ユーザガイドでは VerilogHDL シミュレータである ICARUS Verilog (以下 iVerilog) を使ったシミュレーションが提案されていますので、その手法を試してみます。

(Efinity から iVerilog を実行することができます)

参考ドキュメント

Efinity Software User Guide : UG-EFN-SOFTWARE-v14.1

Chapter 7 Simulating

https://www.efinixinc.com/docs/efinity-ug-v14.1.pdf

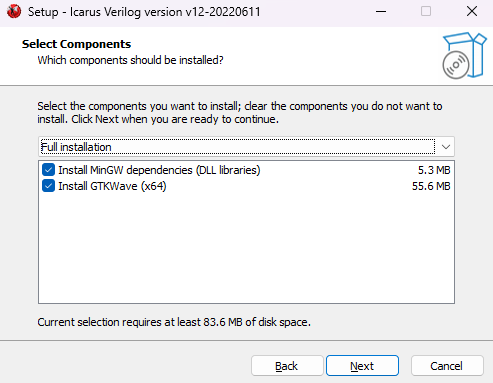

ICARUS Verilog のインストール

まず ICARUS Verilog を We bサイトからダウンロードします。

Windows の場合は下記 URL からダウンロードします。

Linux の場合は apt で取得できるようです。

sudo apt install iverilog

sudo apt install gtkwaveWindows でインストーラを使う場合、別アプリ(コンポーネント) のインストールも勧められるので、これに従います。

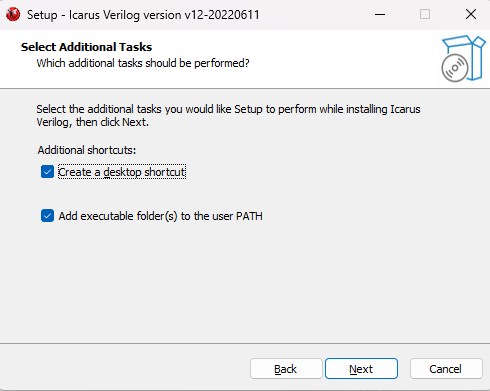

また、デスクトップへのショートカットの作成と、環境変数 PATH への iVerilog インストールフォルダの追加も尋ねられます。ショートカットの作成はどちらでも良いですが、PATH への追加は有効にしてください。

Next, Install ボタンを押して画面を進めて、下図の画面が表示されたらインストール完了です。

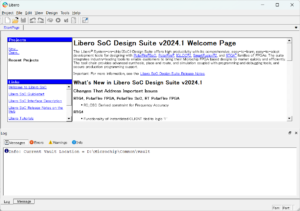

Efinity プロジェクトの準備

シミュレーションを実行する Efinity プロジェクトを用意します。

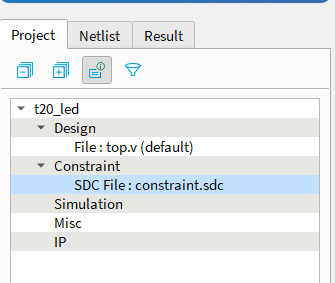

今回は下図のように top.v と top.sdc だけを追加したプロジェクトを用意しました。

それぞれのファイル内容は下記のとおりです。

シミュレーションの DUT は top.v です。

また、top.v には Trion の RAM プリミティブである EFX_RAM_5K を実装しています。

//top.v

module top(

input CLK,

input RSTN,

input WE,

input RE,

output LED,

output [7:0] DBGRD

);

reg [31:0] free_cnt;

reg r_we;

reg r_re;

reg [7:0] r_waddr;

reg [7:0] r_raddr;

wire [7:0] w_rdata;

always@(posedge CLK)

begin

if (RSTN==1'b0)

free_cnt <= 0;

else

free_cnt <= free_cnt + 1;

end

always@(posedge CLK)

begin

if (RSTN==1'b0) begin

r_we <= 1'b0;

r_re <= 1'b0;

end else begin

r_we <= WE;

r_re <= RE;

end

end

always@(posedge CLK)

begin

if (RSTN==1'b0) begin

r_waddr <= 8'h0;

r_raddr <= 8'h0;

end else begin

if (r_we) r_waddr <= r_waddr + 8'h1;

if (r_re) r_raddr <= r_raddr + 8'h1;

end

end

EFX_RAM_5K # (

.READ_WIDTH(8), // 8 256x8

.WRITE_WIDTH(8), // 8 256x8

.OUTPUT_REG(1'b1), // 1 add pipe-line read register

.RCLK_POLARITY(1'b1), // 0 falling edge, 1 rising edge

.RE_POLARITY(1'b1), // 0 active low, 1 active high

.WCLK_POLARITY(1'b1), // 0 falling edge, 1 rising edge

.WE_POLARITY(1'b1), // 0 active low, 1 active high

.WCLKE_POLARITY(1'b1), // 0 active low, 1 active high

.WRITE_MODE("READ_FIRST") // Output "old" data

) EFX_RAM_5K_inst (

.RDATA(w_rdata), // Read data output

.RADDR(r_raddr), // Read address input

.RCLK (CLK), // Read clock input

.RE (r_re), // Read-enable input

.WDATA(free_cnt), // Write data input

.WADDR(r_waddr), // Write address input

.WCLK (CLK), // Write clock input

.WE (r_we), // Write-enable input

.WCLKE(1'b1) // Write clock-enable input

);

assign LED = (w_rdata==8'h0) ? 1'b1 : 1'b0;

assign DBGRD = w_rdata;

endmodule

----

#constraint.sdc

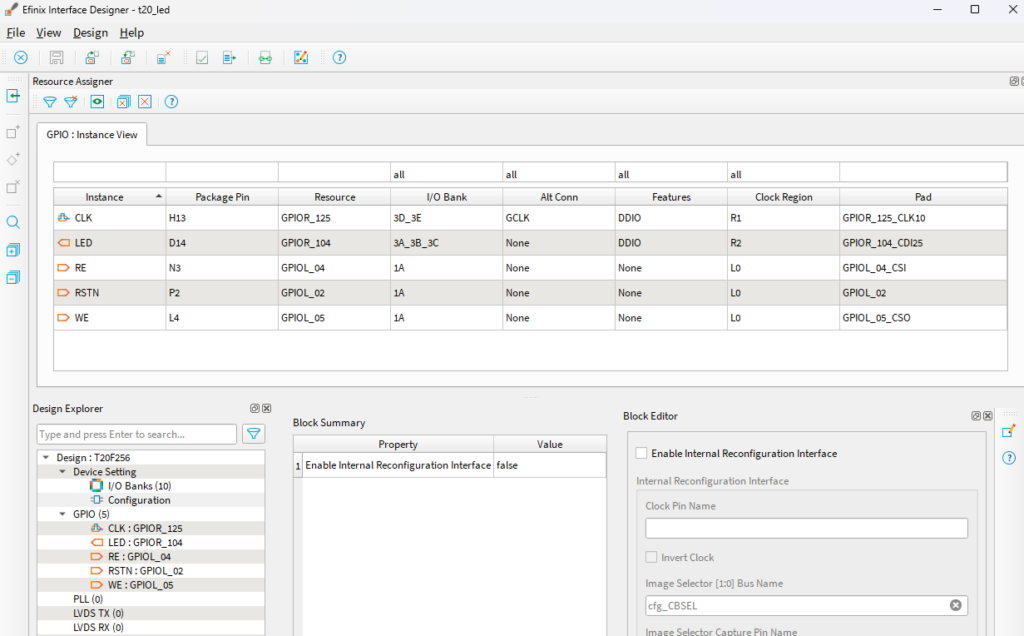

create_clock -period 50 [get_ports {CLK}]Interface Designer の設定

※シミュレーションとは無関係なので適当に設定しています。

テストベンチの用意

top.v のテストベンチを作成します。(ファイル名は top_tb.v )

今回は期待値(結果)比較などはしておらず、クロックとリセット、イネーブル信号を生成して DUT に与えるだけです。

また、テストベンチの下の方に $dumpfile と $dumpvars 文があります。

この 2 つの文によって、シミュレーション波形が .vcd ファイルに出力されます。

//top_tb.v

`timescale 1ns / 1ps

module top_tb;

reg CLK;

reg RSTN;

reg WE;

reg RE;

wire LED;

wire [7:0] DBGRD;

always begin

#5 CLK = 0;

#5 CLK = 1;

end

initial begin

RSTN = 0;

WE = 0;

RE = 0;

#20;

RSTN = 1;

#20;

WE = 1;

#50;

RE = 1;

end

top top_inst(

.CLK(CLK),

.RSTN(RSTN),

.RE(RE),

.WE(WE),

.LED(LED),

.DBGRD(DBGRD)

);

initial begin

$dumpfile("top_tb.vcd");

$dumpvars(0, top_tb);

#1000;

$finish;

end

endmodule;作成したテストベンチは Efinity プロジェクトフォルダの配下に置いておきます。

シミュレーションの実行

(1) Windows のコマンドプロンプトを開きます。

(2) cd コマンドで先ほど用意した Efinity プロジェクトに移動します。

(3) 次のコマンドを実行します。

> (Efinity インストールフォルダ)\bin\efx_run.bat (プロジェクト.xml) --flow rtlsim --tb (テストベンチファイル名) --tb_top (テストベンチモジュール名)

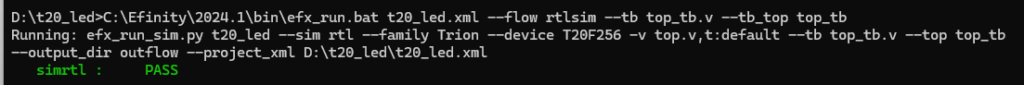

Efinity 2024.1 でプロジェクトを作った場合は、下記のようなコマンドになります。

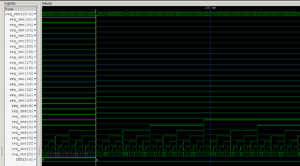

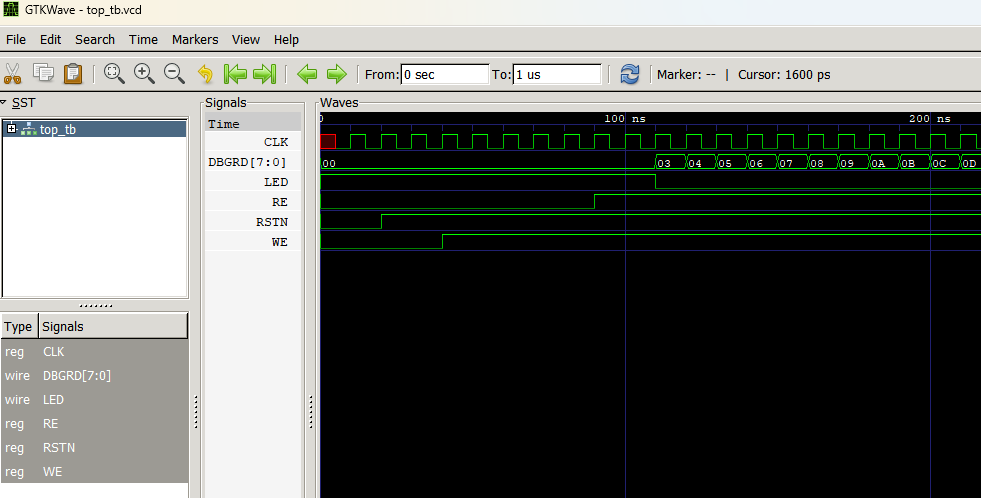

>C:\Efinity\2024.1\bin\efx_run.bat t20_led.xml --flow rtlsim --tb top_tb.v --tb_top top_tb(4) シミュレーション結果(PASS) が表示されたら成功です。gtkwave コマンドを実行すると波形を確認できます。

Efinity の Trion FPGA のプリミティブである EFX_RAM_5K のシミュレーションモデルも自動的にコンパイルされて、期待通り動作しています。

gtkwave top_tb.vcd

論理合成結果のシミュレーション

上記シミュレーションは RTL シミュレーションでしたが、Efinity では論理合成結果のシミュレーションにも対応しています。

Efinity で論理合成(Synthesis) を実行すると、論理合成結果が .map.v という VerilogHDL ファイルで出力されます。

さきほどのシミュレーションコマンドの引数を変えることで、.map.v をシミュレーションの DUT として使うことができます。

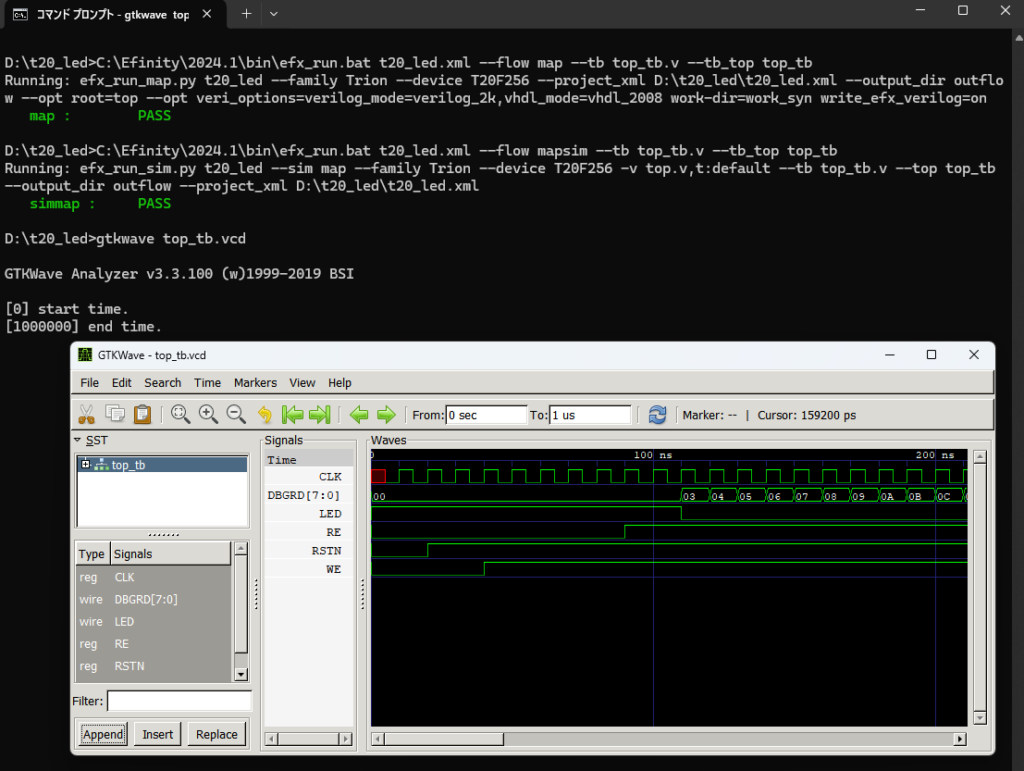

(1) 下記のコマンドで論理合成を実行します。(--flow を map にします)

> (Efinity インストールフォルダ)\bin\efx_run.bat (プロジェクト.xml) --flow map --tb (テストベンチファイル名) --tb_top (テストベンチモジュール名)

※論理合成プロセスが実行されるので、完了まで少し時間がかかります。

(2) 論理合成が終わったら下記のコマンドでシミュレーションを実行します。(--flow を mapsim にします)

> (Efinity インストールフォルダ)\bin\efx_run.bat (プロジェクト.xml) --flow mapsim --tb (テストベンチファイル名) --tb_top (テストベンチモジュール名)

実行例

Efinity シミュレーションの利点・注意点

Efinity でシミュレーションを実行すると、Efinix FPGA の Primitive シミュレーションモデルが自動的に組み込まれるのが便利です。

ちなみに、Primitive シミュレーションモデルは Efinity のインストールフォルダに格納されているので、これらを他のシミュレーションソフト (Questa, Riviera, NCsim ... etc.) に持っていってシミュレーションすることもできます。

注意点としては、2024年8月現在、Efinity では配置配線後のシミュレーションには対応していません。

※「配置配線の妥当性はタイミング解析によって確認」というスタンスですね。