Efinix Ti60 評価ボードでLチカ 後編 (実装)

前回に引き続き Efinix Ti60 評価ボードで L チカにトライします。

コンパイル作業は Efinity の Efinity IDE 2023.2 を使っていきます。

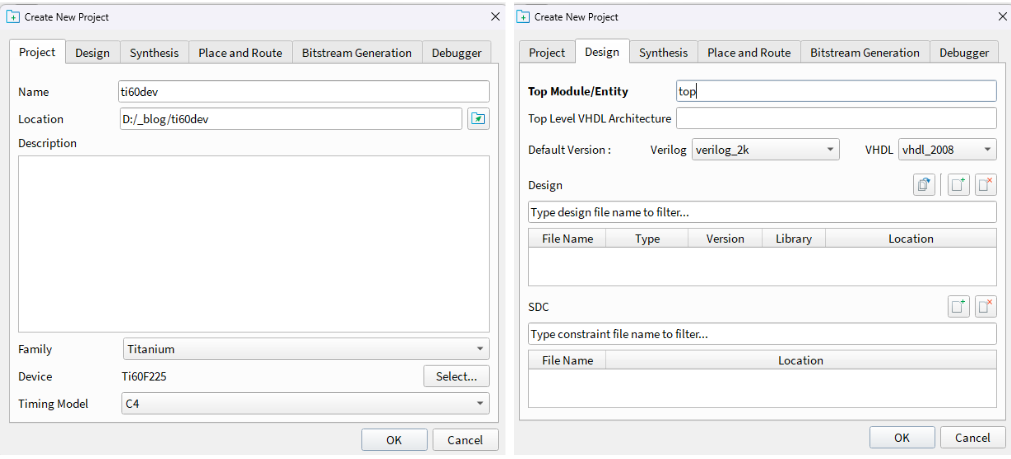

1. Efinity プロジェクトの作成

まず Efinity でプロジェクトを作成します。

(1) File - Create Project を選択します。

(2) Project タブで Name と Location を設定し、Device は Ti60F225 を選択します。

続いて Design タブでは Top Module/Entity に top と入力します。

Top Module の指定が空欄でも Efinity は自動的に Top Module を判別してくれますが、ソースコード (ファイル) が増えてくると自動判別の精度が落ちるので、明示的に手動指定したほうが良いです。

Synthesis 以降のタブは今回は設定不要なのでスキップします。

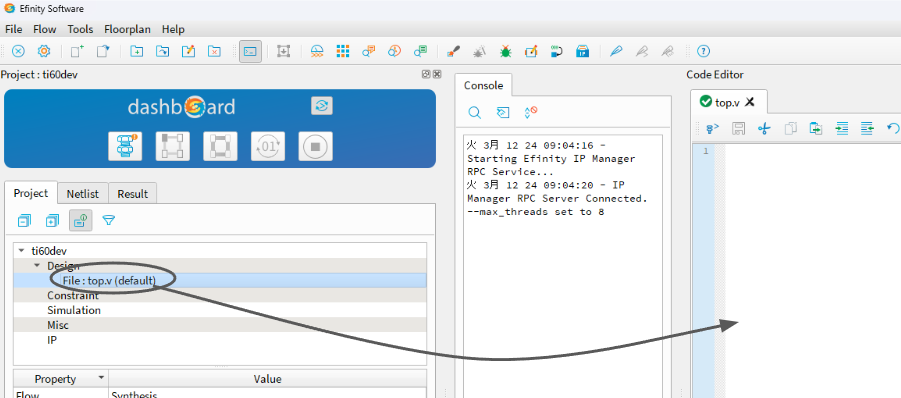

2. VerilogHDL コードの記述

LED 点滅の Verilog HDL コードを記述していきます。

※ Efinity は VHDL にも対応しています。

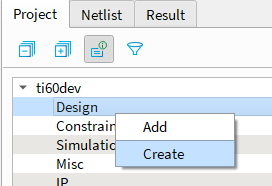

(1) Project タブの "Design" を右クリックして Create を選択します。

(2) File Name に top と入力して OK を押します。

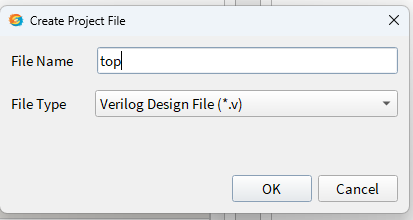

(3) Project タブの top.v をダブルクリックして top.v を開きます。

Tips

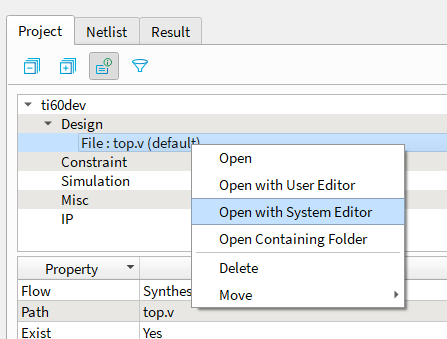

ちなみに top.v を右クリックして "Open with System Editor" を選択すると、Windows で .v ファイルに関連付けられているエディタでファイルを開くことができます。普段使っているエディタで編集したいときに便利です。

(4) コードを記述します

CLK は 100MHz クロックです。

nRST は Active Low のリセット信号で、基板上のタクトスイッチからの入力を受け取ります。

Ti60 DevKit に搭載されている LED は 3 色 LED なので、出力 OLED は 3 ビットにしてみました。

top.v

module top

(

input CLK,

input nRST,

output [2:0] LED

);

reg [29:0] reg_cnt;

always@(posedge CLK)

begin

if (!nRST)

reg_cnt <= 30'h0;

else

reg_cnt <= reg_cnt + 30'h1;

end

assign LED = reg_cnt[29:27];

endmodule(5) 仮コンパイル

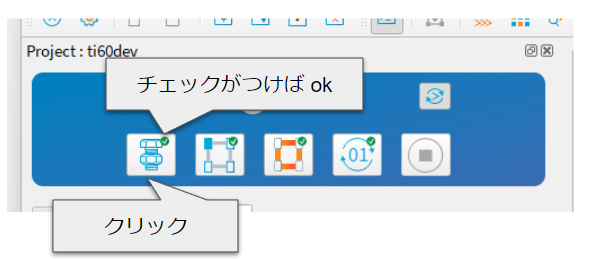

ピン設定やタイミング制約記述が未完了ですが、いったん仮でコンパイルしてみましょう。

Synthesis プロセスにチェックマークが付けば ok です。

3. Interface Designer の設定

次に FPGA の外ピンと、top.v の I/O ポートを結びつける設定をしていきましょう。

Efinity では Interface Designer というツールを使ってピンの設定をしていきます。

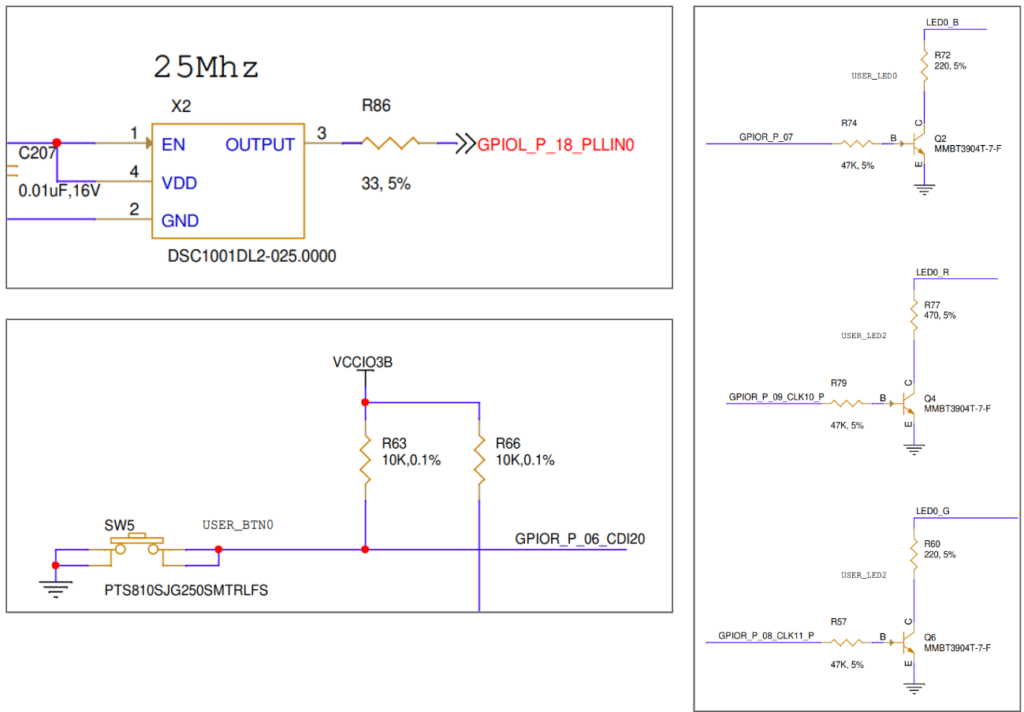

ピンの選定

Interface Designer を起動する前に、まずは Ti60 評価ボードの回路図を見て、I/O ポートをどのピンに割り当てるか決めていきましょう。

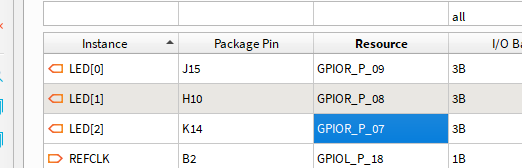

今回は下記のピンを使うことにします。

- クロック : 25 MHz GPIOL_P_18

- FPGA 内の PLL で 100MHz に逓倍します

- リセット : SW5 GPIOR_P_06

- LED_B : GPIOR_P_07

- LED_R : GPIOR_P_09

- LED_G : GPIOR_P_08

※下図はいずれも Efinix 公式サイトからの引用です

クロックピンとPLL の設定

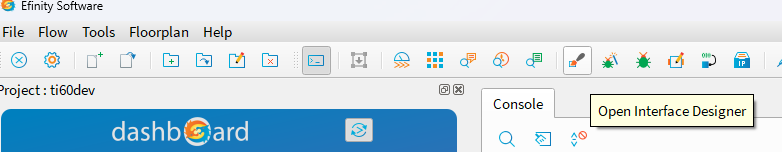

ここから実際に Interface Design を使って設定を進めていきます。

(1) まず Efinity でのツールバーから Open Interface Designer を選択します。

クロックピン (リファレンスクロック) の設定

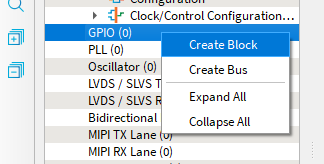

(2) GPIO を右クリックして Crete Block を選択します。

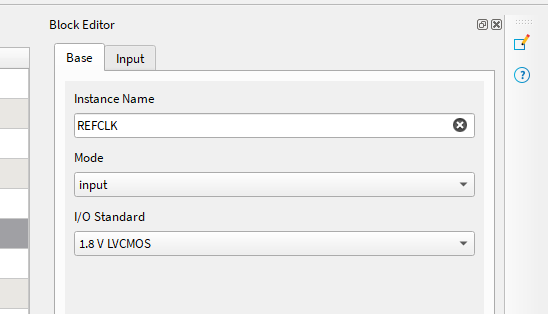

(3) Instance Name に REFCLK と入力し、Mode を Input にします。

注意

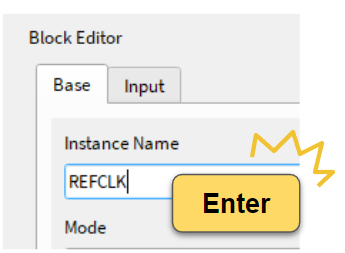

テキストボックスに文字を入力したら、いちど Enter キーを押しましょう。

Enter キーを押さずに別のタブに移動すると、入力したテキストが反映されていないことがあります。

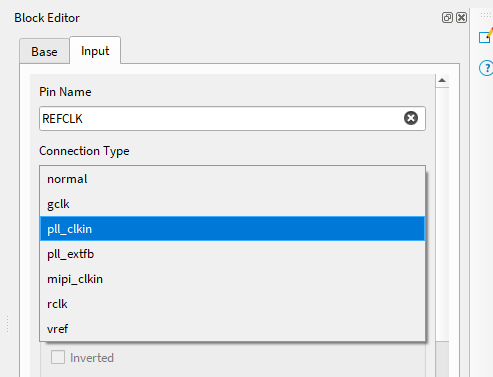

(4) Input タブで Connection Type を pll_clkin に設定します。

Tips

Efinix のクロックピンは、gclk と pll_clkin の 2 種類があります。

gclk は、クロックバッファーを介して Logic Block に直接つながっています。

pll_clkin は、PLL のリファレンスクロックポートにつがっており、Logic Block にはつながっていません。

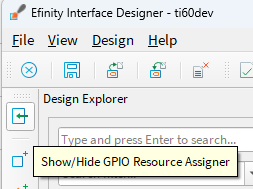

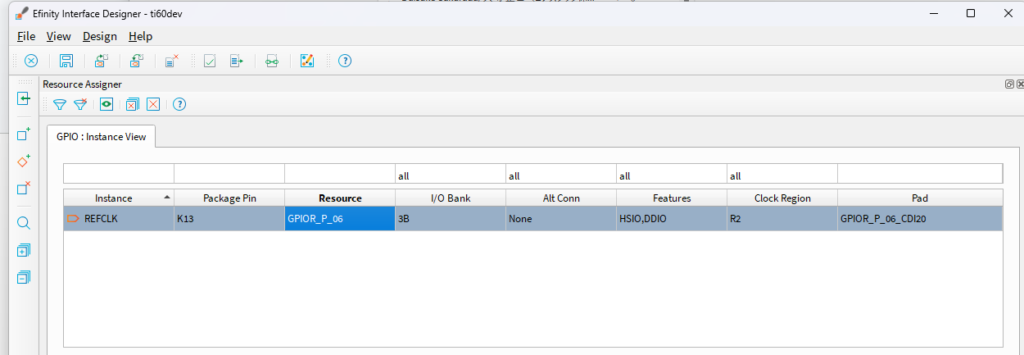

(5) Show /Hide GPIO Resource Assigner を押します。

(6) REFCLK の Resource に GPIOR_P_06 と入力します。

PLL の逓倍設定

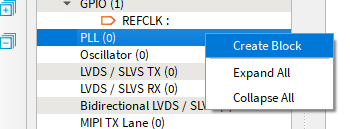

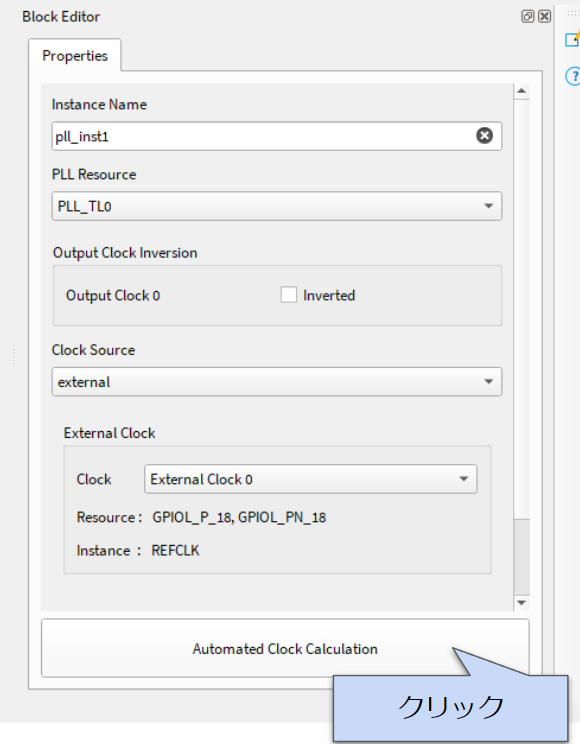

(7) PLL を右クリックして Create Block を選択します。

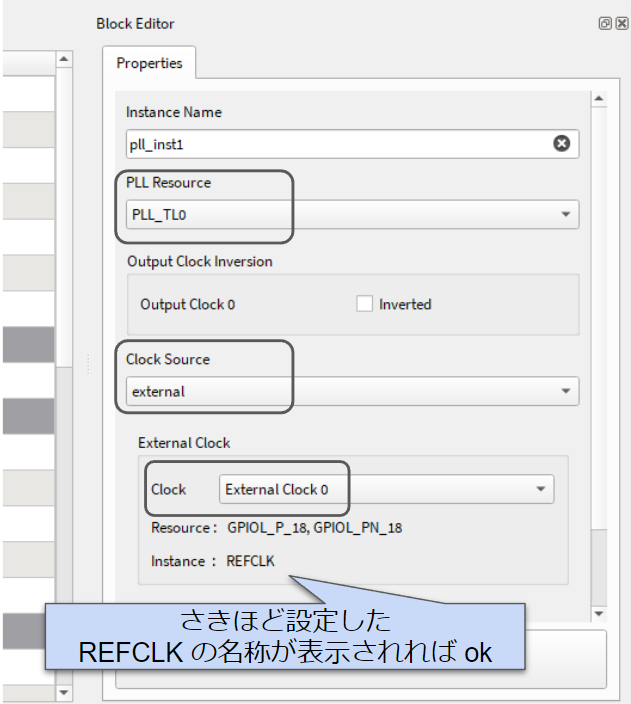

(8) PLL Resource は PLL_TL0 を選択し、External Clock 0 を選択します。

このとき Instance として、(3) で入力した "REFCLK" の名称が表示されていれば ok です。

(9) Automated Clock Calculation ボタンを押します。

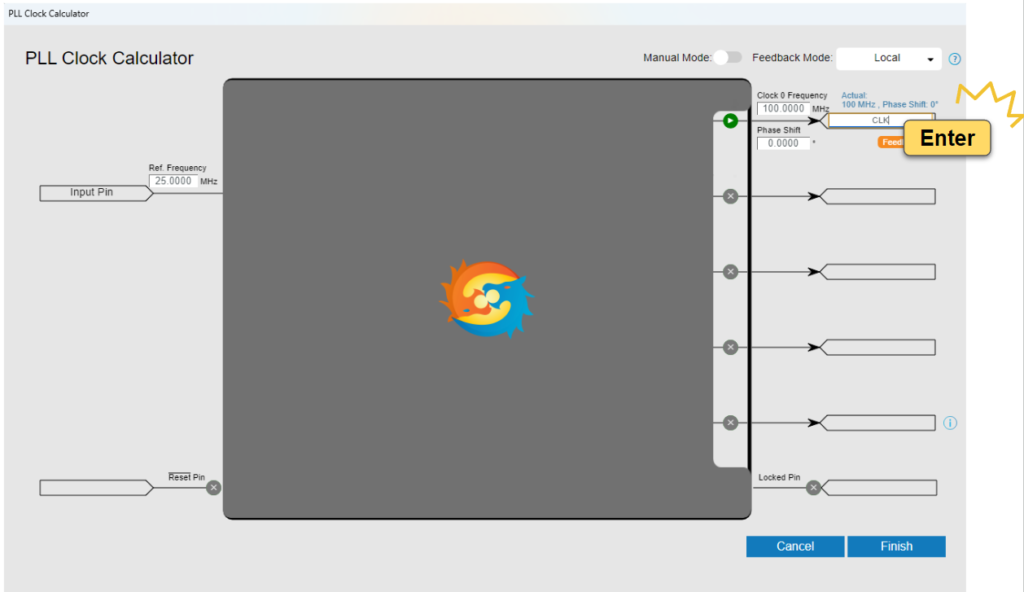

(10) PLL の設定画面が現れるので、下図のようにテキストボックスに入力します。

テキストを書き換えた箇所では Enter キーを忘れずに押してください。

書き換えが終わったら画面右下の "Finish" を押します。

これで 25 MHz のクロックを逓倍して 100 MHz を生成できます。

右端のボックスに入力した "CLK" が、Verilog HDL の top で宣言した "CLK" と紐づけられます。

この PLL 設定画面と Verilog HDL のポート名が異なっていると紐づけができないので注意してください。

Tips

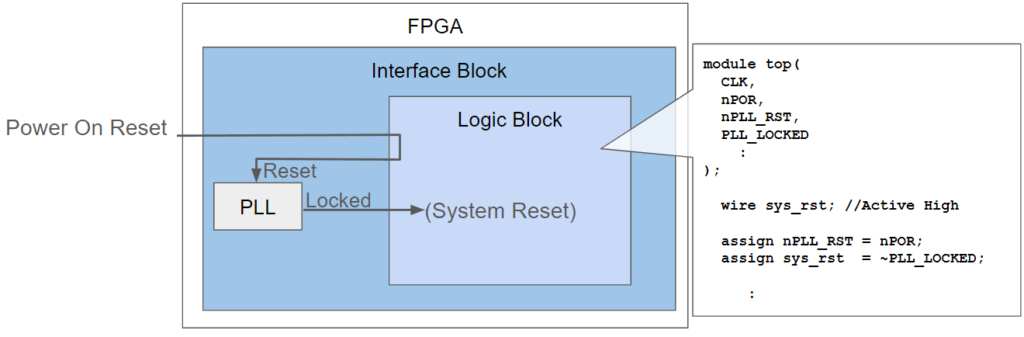

今回は Reset / Locked Pin を使いませんが、製品設計の際はリセットシーケンスの一部として使うことをお勧めします。

Reset ピンには FPGA 外部の Power On Reset を入力し、Locked ピン出力は Verilog HDL のリセットに接続するイメージです。

実装例)

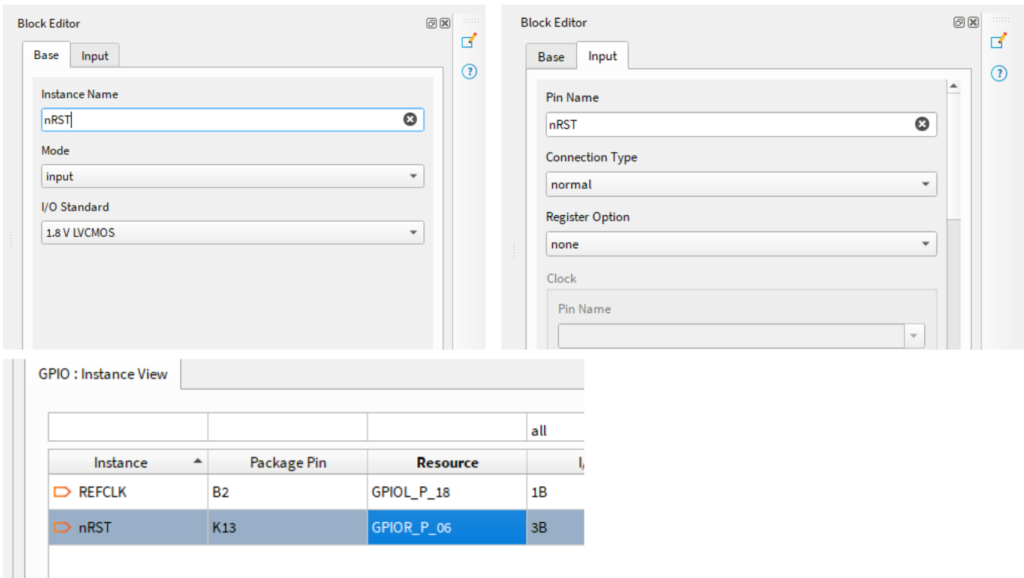

リセットと LED ピンのアサイン

つぎに、リセットと LED のピンアサインを進めていきます。

リセットはさきほどのクロック入力と同様に GPIO - Create Block で追加します。

LED は GPIO - Create Bus で追加します。

リセットの追加

LED の追加

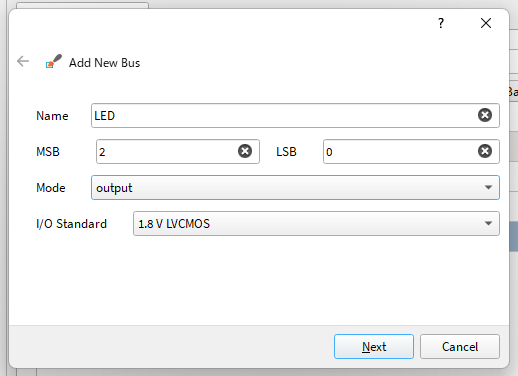

Create Bus を選択した場合は下図のようなポップアップが表示されるので、ここで Name, バス幅, Mode を設定していきます。

Check Design

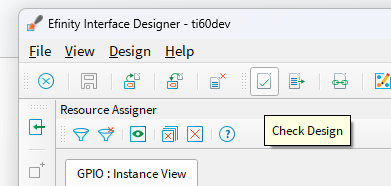

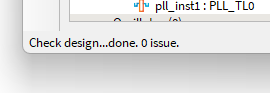

一通り Interface Desginer での設定が終わったら "Check Design" ボタンを押します。

これを押して 0 issue になっていれば ok です。

タイミング制約テンプレートの生成

あとはタイミング制約を記述してコンパイルを実行すればよいのですが、Interface Designer でタイミング制約のテンプレートを生成できるので、これを使うのが便利です。

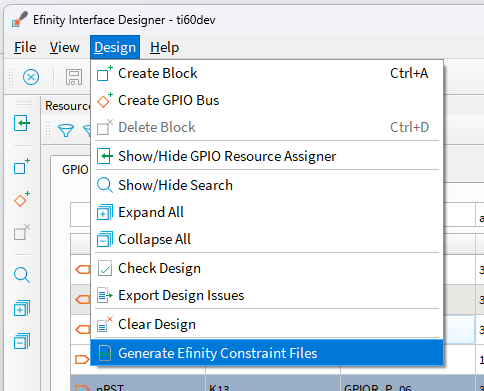

(1) Interface Designer の Design - Generate Efinity Constraint Files を押します。

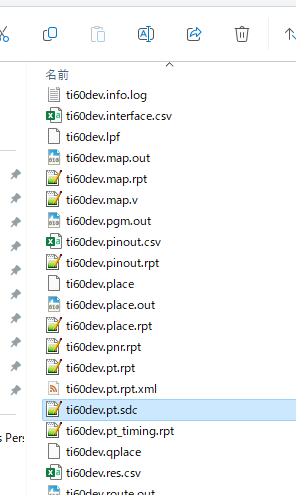

(2) プロジェクトの Outflow フォルダ配下に .pt.sdc ファイルが出力されていることを確認します。

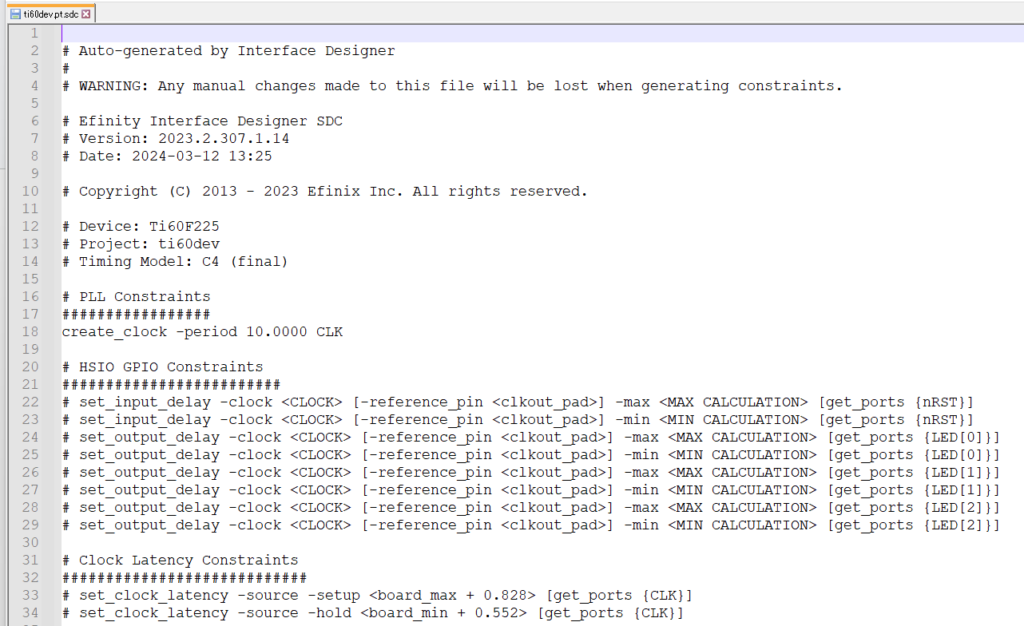

.pt.sdc はこのようになっています。

PLL で定義したクロックの制約に加えて、入出力制約 (input delay, output delay) のテンプレが記述されています。

今回は入出力制約は省略して、クロック制約だけ使うことにします。

4. タイミング制約の記述

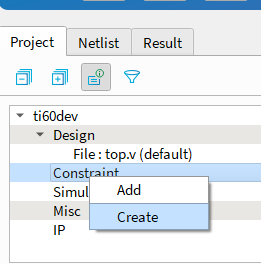

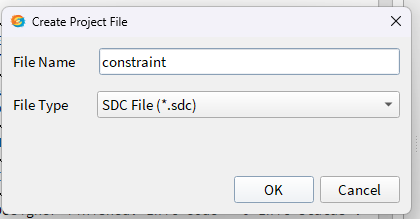

Efinity に戻って、Constraint を右クリックして Create を選択します。

ファイル名は "constraint" にします。

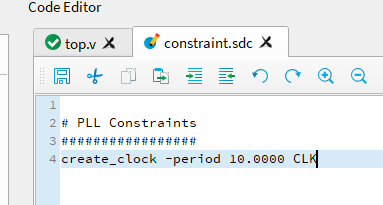

生成された constraint.sdc ファイルを開いて、さきほど生成したタイミング制約テンプレート (.pt.sdc) の create_clock 制約をコピペします。

5. コンパイルと結果の確認

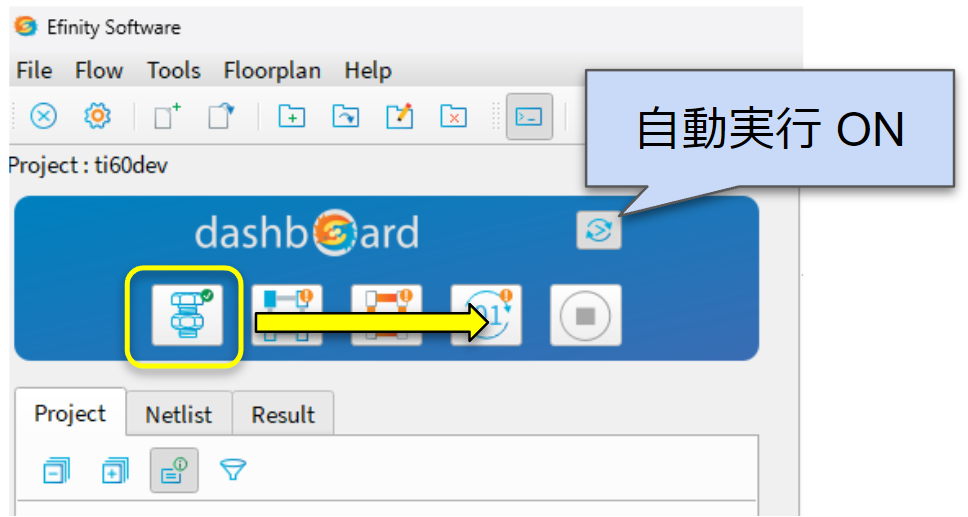

タイミング制約の記述まで終わったら、Efinity dashboard の Synthesis ボタンを押します。

自動実行ボタンが ON になっていれば、Placement, Routing, Generate Bitstream まで自動的に進みます。

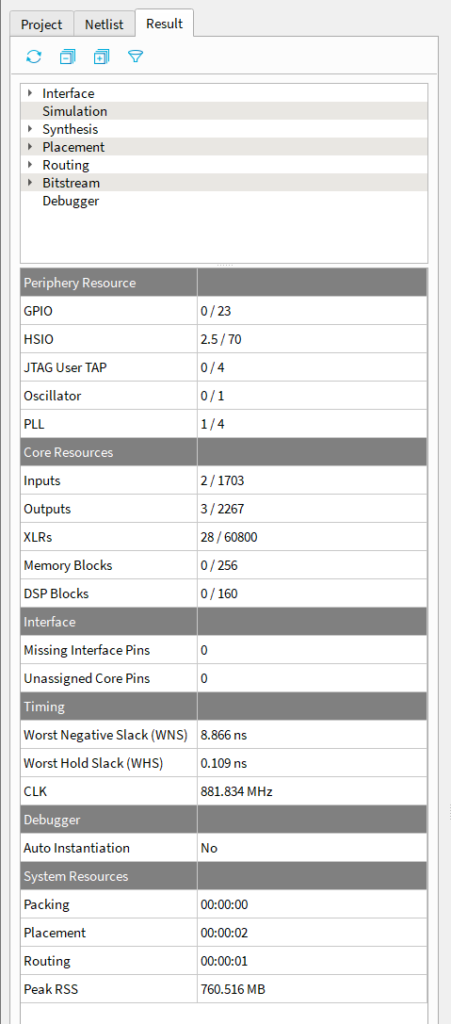

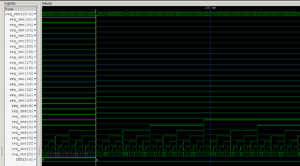

Efinity の Result タブを開くとコンパイル結果を閲覧できます。

ここまで手順通り操作していれば、下図のようになるはずです。

※Efinity のバージョンや PC によっては、Timing の数値が変動することがあります。

6. Bitstream の書き込み (実機動作確認)

Generate Bitstream までエラーなく終了したら、実際に Ti60 評価ボードに書き込んで動作確認してみます。

書き込むファイルは .bit と .hex のいずれかです。

- .bit ファイル

FPGA の JTAG ポートをつかって FPGA に直接 bitstream をプログラムします。

電源を切ると揮発します。 - .hex ファイル

基板上の SPI Flash Memory に bitstream をプログラムします。

基板の電源が投入されて FPGA が起動すると、FPGA は SPI Flash Memory にアクセスして bitstream をロードし、自分自身にプログラムします。

では実際に書き込んでみます。

(1) Ti60 評価ボードの電源を ON にします。

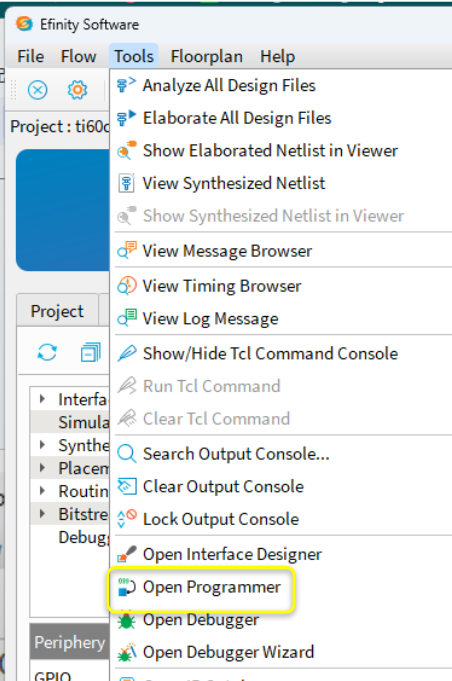

(2) Efinity の Tools - Open Programmer を選択します。

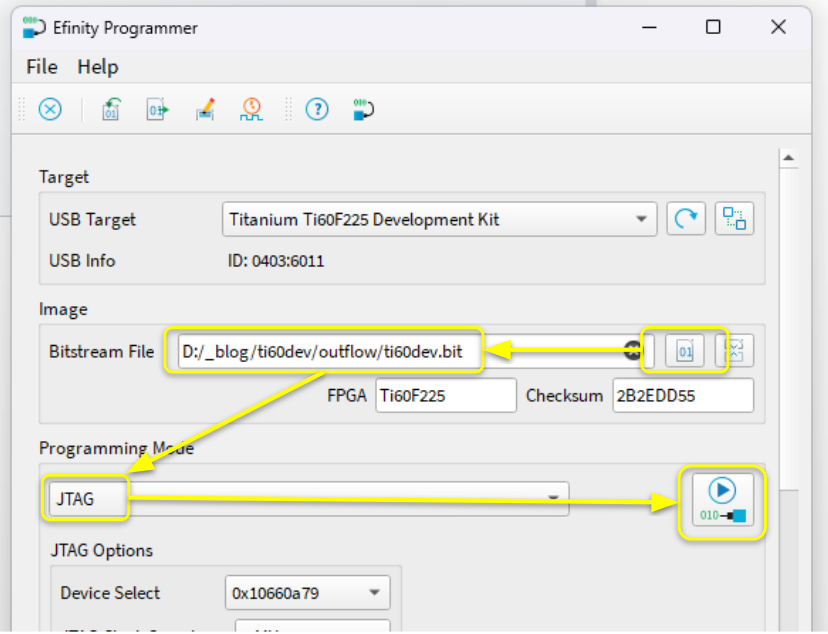

(3) Bitstream File として outflow フォルダ配下の .bit ファイルを選択し、Programming Mode を JTAG にして Start Program を押します。

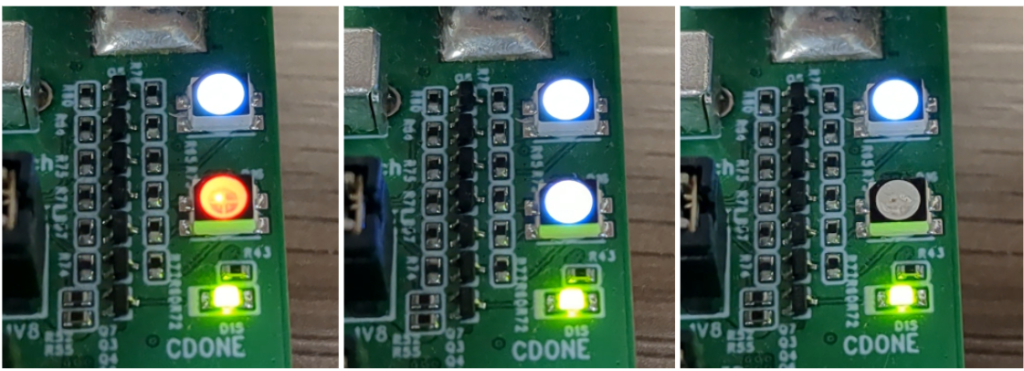

(4) 基板上の LED がチカチカ色を変えながら点滅していれば ok です

hex ファイルの書き込み

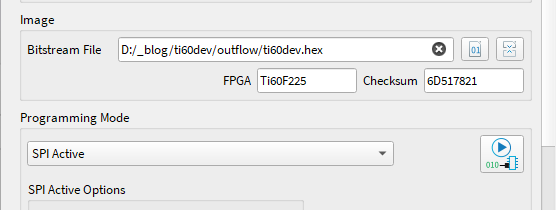

ちなみに hex ファイルを書き込むときは Programming Mode を "SPI Active" にします。

まとめ

以上で L チカ記事は終了です。

これで、Efinity での作業フローを網羅できたので、次回は Efinity の Debugger 機能 (ロジアナ, 仮想 I/O) を使ってみたいと思います。

“Efinix Ti60 評価ボードでLチカ 後編 (実装)” に対して1件のコメントがあります。