Efinix Ti60 評価ボードでLチカ 前編 (準備)

みなさん、こんにちは。サクラダです。

FPGA エンジニアとして、皆様の役に立つような情報を発信したいと思い技術ブログを始めました。

さて記念すべき 1 回目は Efinix 社の FPGA を取り上げます。

Efinix の FPGA には第一世代の Trion シリーズと、第二世代の Titanium シリーズがあります。

Trionシリーズはラインナップがほぼ固まりつつある印象ですが、Tinitaium シリーズは Serdes 搭載品や RISC-V (CPU) ハードマクロ搭載品が予定されているなど、進化が続いています。

※FPGA 設計者の視点で言うと、Titanium のほうが少々高価ではありますが Fmax を高く取れるのでオススメです。

今回の記事では、そんな Tinitanium シリーズの Ti60 F225を使って L チカに挑戦してみます。

Titanium FPGA の構成

L チカの実装に取り掛かる前に、Efinix デバイスの特徴的な構成を知っておく必要があります。

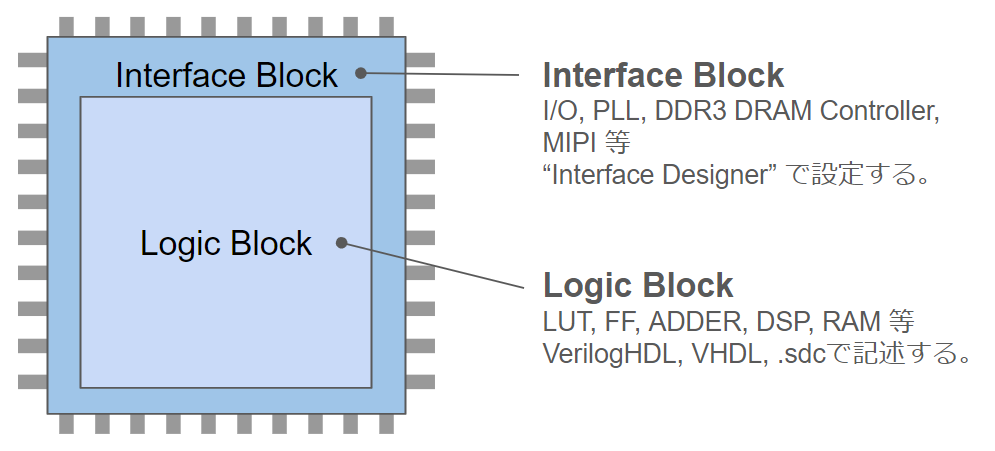

Efinix デバイスは下図のように、"Interface Block" と "Logic Block" の 2 つで構成されています。

- Interface Block (インタフェースブロック)

- I/O, PLL, DDR3 SDRAM Controller, MIPI などのハードマクロが実装されているエリア。

- Interface Designer という GUI ツールをつかって、使いたいハードマクロの設定をする。

- I/O ピン配置, 電圧設定もこのブロックで行なう。

- Logic Block (ロジックブロック)

- LUT, FF, ADDER(加算器), DSP, RAM 等のプリミティブが実装されているエリア。

- Verilog HDL(SystemVerilog 含む), VHDL で記述する。

- タイミング制約 (.sdc) の記述も必要。

Intel 社や AMD 社のデバイス・ツールであれば、たとえば、PLL や DRAM Constoller のインスタンスを Verilog HDL のトップデザインに記述しますが、Efinix ではそれができません。

ただ、"設計資産"の観点で考えると、ハードブロックとソフト(ロジック)ブロックが明確に区別されることで、ソフト側(ソースコード) の再利用性・移植性が良くなります。

DSP や RAM 等のプリミティブを推論記述にしておくことで、ソースコードを丸ごと別の FPGA デバイスにも移植できますし、個人的には好みの設計思想です。

Ti60 Development Board の構成

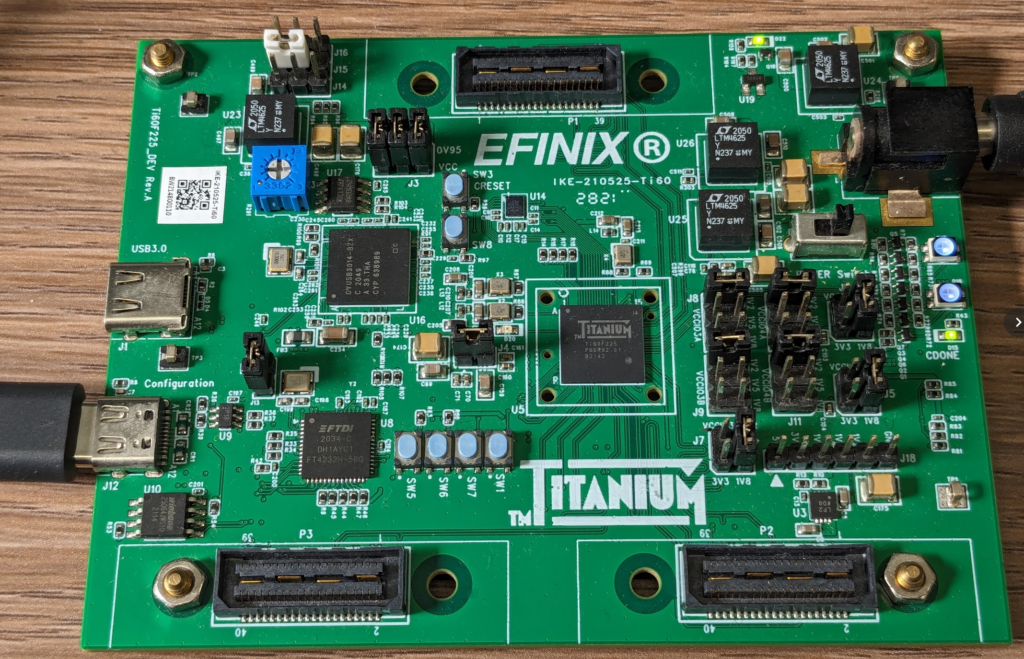

Ti60 評価ボードにはこのような付属品が同梱されています。

- DSI LCD

- Rapsberry PI Camera v2 (ラズパイカメラ)

- QSE - 2.54 mm ピンヘッダ ドーターカード

- AC/DC アダプタ (12V)

- USB-C ケーブル

LCD は使用前に電圧調整の作業が必要です。この手順を踏まずに評価ボードに接続すると破損するので注意してください。

その他の同梱品については公式サイトを参照してください。

https://www.efinixinc.com/products-devkits-titaniumti60f225.html

ちなみに、Ti60 評価ボード (TI60F225C-DK) は国内代理店または DigiKey で購入できます。(2024年2月現在で約 5.6 万円)

技術サポートは、代理店購入の場合は日本人スタッフ、DigiKey 購入の場合は海外公式サイトだけになってしまうので注意が必要です。

代理店については公式サイトを参照してください。

https://www.efinixinc.com/jp/company-distributors.html

ソフトウェア・ライブラリのインストール

Ti60 評価ボードを使う上で必要になるソフトウェア・ライブラリ・ドライバ類は下記のとおりです。

- Oracle Java 8 or OpenJDK

- Microsoft Visual C++ 2019 x64 runtime library redistributable (2019 以降)

- Efinix Efinity IDE 2023.2

- Zadig 2.8

Java と Visual C++ runtime library は Efinity の実行に必要です。

Zadig は、Efinity から Efinix FPGA に JTAG アクセスしたり、Flash Memory にビットストリームを書き込んだりするときに必要です。

ドライバ (libusb) のインストール

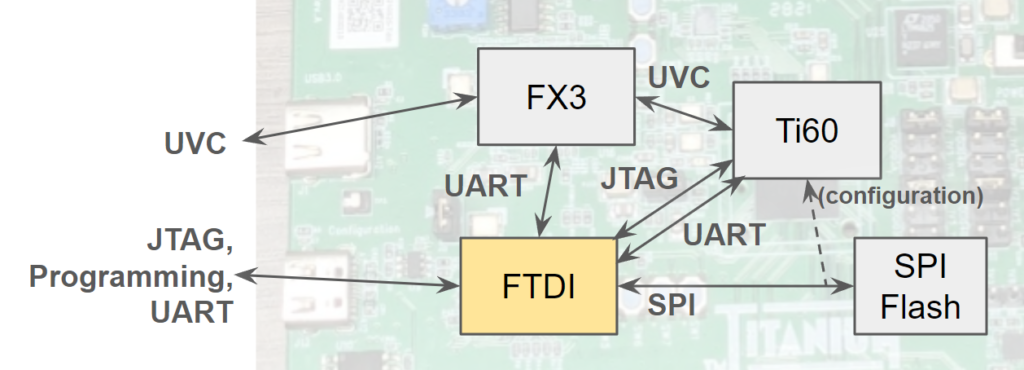

Ti60 評価ボードには FTDI 社のチップが搭載されており、FTDI チップには下図のようにバスが割り当てられています。

この FTDI チップを介して下記の機能を使用できます。

- Efinity Programmer による Ti60 FPGA への bit stream 書き込み

- Efinity Programmer による SPI Flash Memory への bit stream 書き込み

- Efinity Debugger による Ti60 FPGA 上のロジアナ / 仮想 IO へのアクセス

- Terminal (TeraTerm等) による Ti60 との UART 通信 (UART ロジックの実装が必要)

- Terminal (TeraTerm等) による FX3 デバイスとの UART 通信

Efinity では FTDI チップと通信するために FTDI 社の標準ドライバではなく、libusbk というドライバを使っています。

この libusbK をインストールするために Zadig というツールを使います。

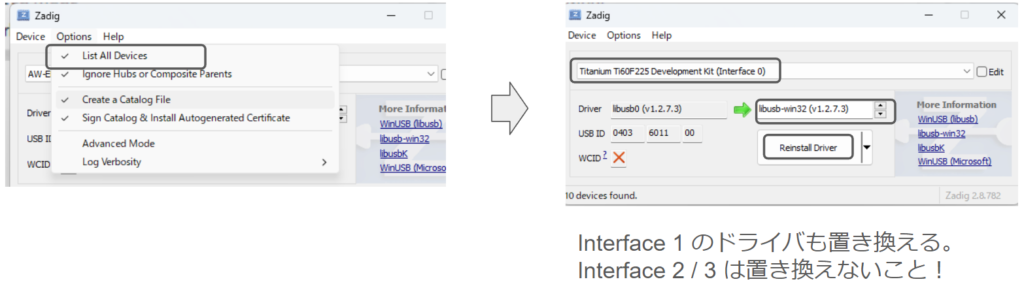

Zadig によるドライバのインストール手順は下記のとおりです。

(1) Ti60 評価ボードと PC を USB-C ケーブルで接続し、Ti60 評価ボードの電源をいれる。

(2) Zadig 2.8 を起動する。

(3) Zadig が起動したら Option - List All Devices にチェックを入れる。

(4) Titanium Ti60F225 Development Kit (Interface 0) を選択する。

(5) libusb-win32 を選択する。

(6) Replace Driver (Reinstall Driver) を押す。

(7) 同様に、Interface 1 に対しても Replace を実行する。

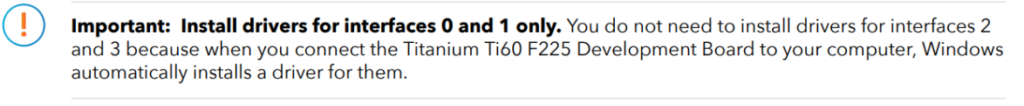

※Interface 2 と Interface 3 のドライバは置き換えないので注意してください。

下図の通り Ti60 Development Board User Guide に記載があります。

libusb のドライバをアンインストールするには

もし libusb のドライバをアンインストールしたい場合は、デバイスマネージャを使ってアンインストールします。

(1) アンインストールしたいデバイスを右クリックして "デバイスのアンインストール" をクリック

(2) "デバイスのドライバーを削除しようとしました。" にチェックを入れて "アンインストール" をクリック

(3) USB ケーブルを抜き差しする

(4) Zadig で当該デバイスの Driver 欄を見る。

(5) "FTDIBUS" になっていればアンインストール完了。なっていなければ (1) ~ (4) の操作を何度か繰り返す。

次回

以上で Ti60 評価ボードを使用するための準備が終わりました。

次回は、ロジックやタイミング制約の記述や I/O アサインを試していきます。

“Efinix Ti60 評価ボードでLチカ 前編 (準備)” に対して2件のコメントがあります。