Efinity Debugger を試す 後編 (Virtual IO 編)

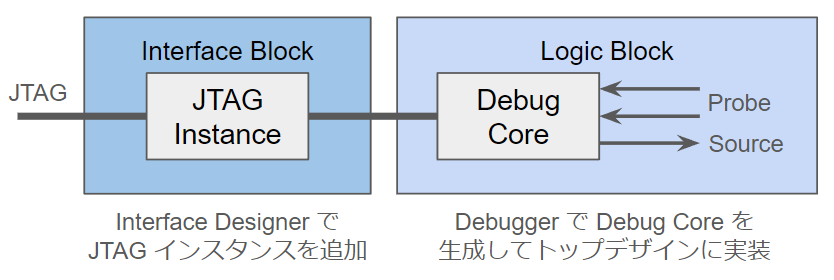

Virtual IO の概要

Efinity Debugger の Virtual IO モードでは、信号への値のセット、信号の値のモニタができます。

Virtual IO のインスタンスは、Verilog HDL (VHDL) のトップデザインに、手動で実装する必要があります。

Debugger で Debug Core を生成する

- Debugger を起動します。

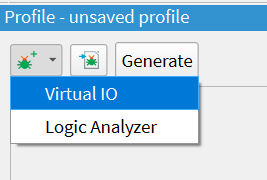

2. Add Debug Core で Virtual IO を選択します。

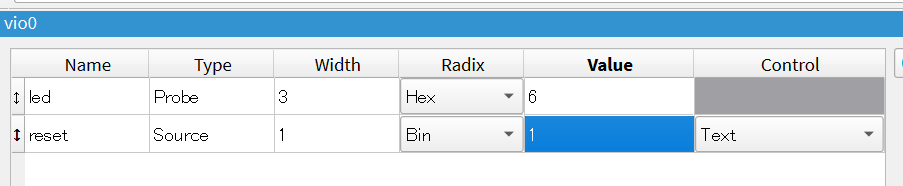

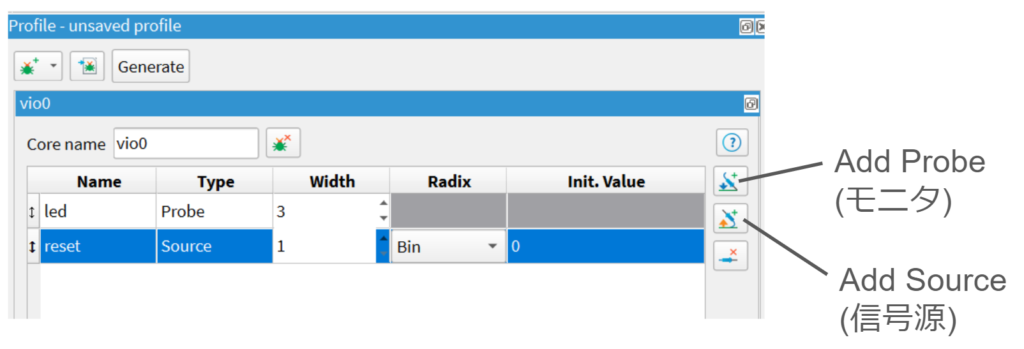

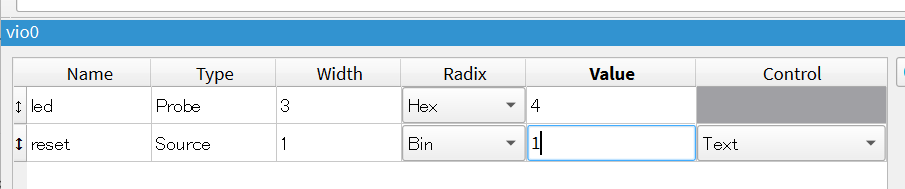

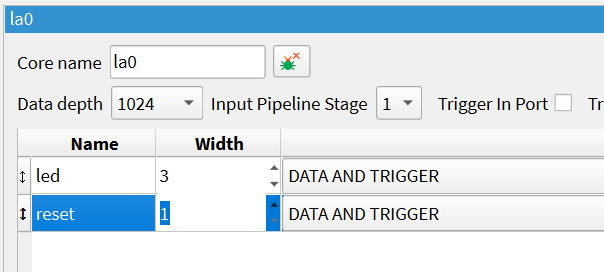

3. Add Probe で led 3ビット, Add Source で reset 1 ビットを追加します。

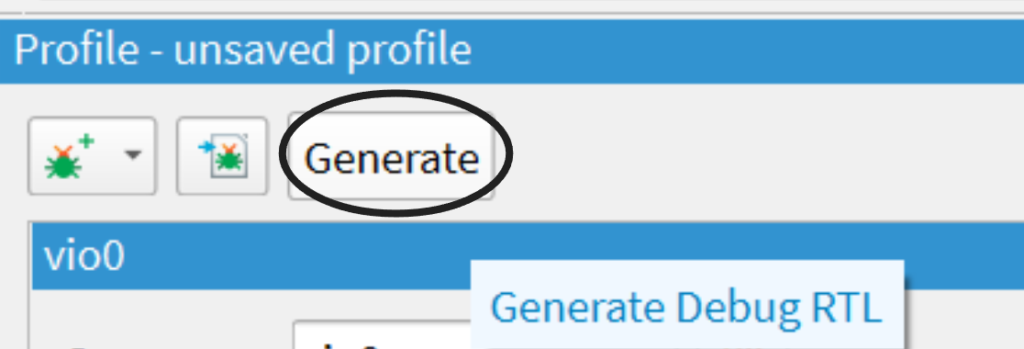

4. Generate を押します。

トップデザインに Debug Core を実装する

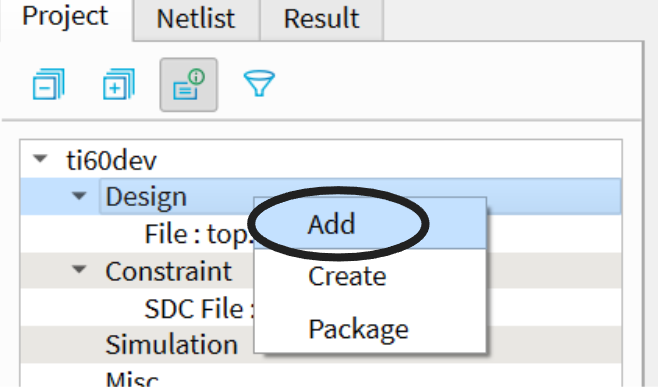

1. Efinity Project の Design を右クリックして Add を選択します。

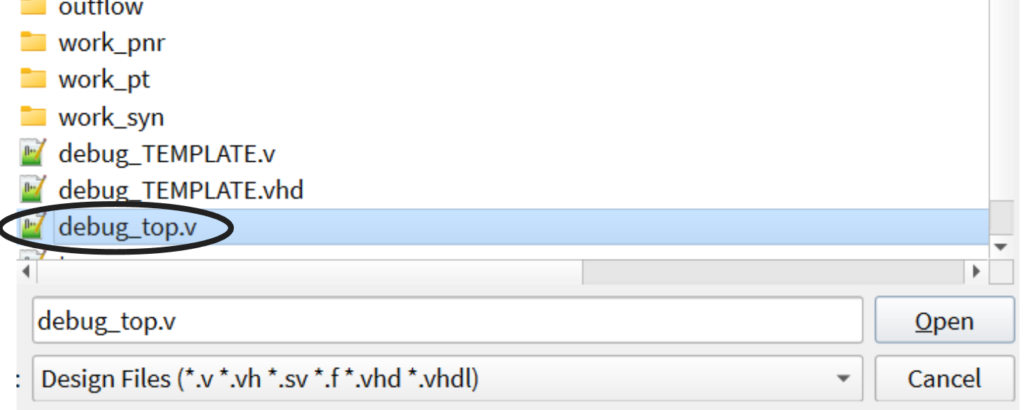

2. debug_top.v を選択します。

3. トップデザインのコードを下記の通り記述します。

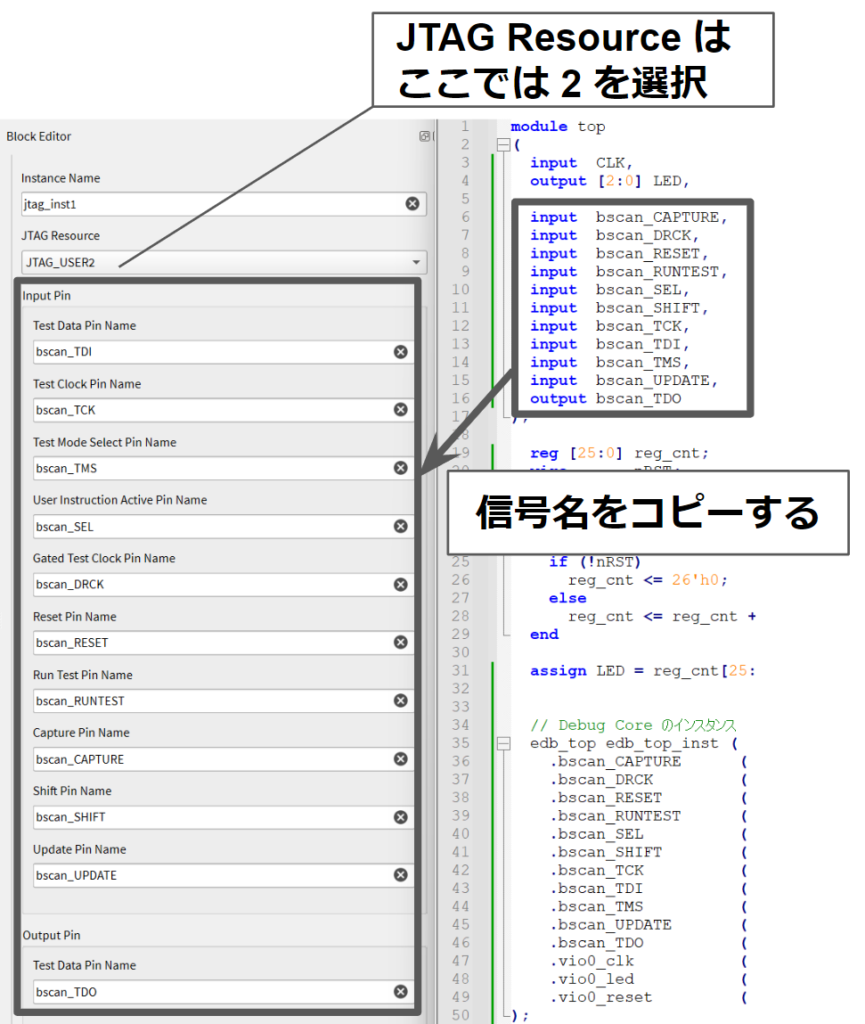

ポイント1 : I/O 宣言に Debug Core 接続用の JTAG インスタンス信号を追加する。

ポイント2 : Debug Core のインスタンスを実装する

top.v

module top

(

input CLK,

output [2:0] LED,

// Debug Core に接続する JTAG インスタンスの信号

input bscan_CAPTURE,

input bscan_DRCK,

input bscan_RESET,

input bscan_RUNTEST,

input bscan_SEL,

input bscan_SHIFT,

input bscan_TCK,

input bscan_TDI,

input bscan_TMS,

input bscan_UPDATE,

output bscan_TDO

);

reg [25:0] reg_cnt;

wire nRST;

wire [2:0] LED;

always@(posedge CLK)

begin

if (!nRST)

reg_cnt <= 26'h0;

else

reg_cnt <= reg_cnt + 26'h1;

end

assign LED = reg_cnt[25:23];

// Debug Core のインスタンス

// debug_top.v のポートに信号を接続する

//

edb_top edb_top_inst (

.bscan_CAPTURE ( bscan_CAPTURE ),

.bscan_DRCK ( bscan_DRCK ),

.bscan_RESET ( bscan_RESET ),

.bscan_RUNTEST ( bscan_RUNTEST ),

.bscan_SEL ( bscan_SEL ),

.bscan_SHIFT ( bscan_SHIFT ),

.bscan_TCK ( bscan_TCK ),

.bscan_TDI ( bscan_TDI ),

.bscan_TMS ( bscan_TMS ),

.bscan_UPDATE ( bscan_UPDATE ),

.bscan_TDO ( bscan_TDO ),

.vio0_clk ( CLK ),

.vio0_led ( LED ),

.vio0_reset ( nRST )

);

endmoduleInterface Designer で JTAG インスタンスを追加する

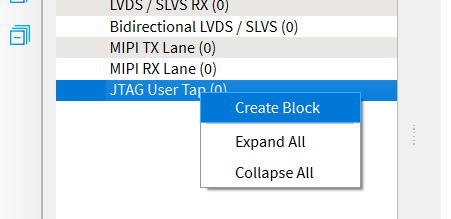

1. Interface Designer を起動します。

2. JTAG User Tap を右クリックして Create Block を選択します。

3. JTAG Resource を USER2 (任意) にし、信号名をトップデザインの信号名を合わせます。

Resource はどれでも良いですが、他の機能 (RISC-V (Sapphire SoC) など) で指定した Resource と競合しないようにします。

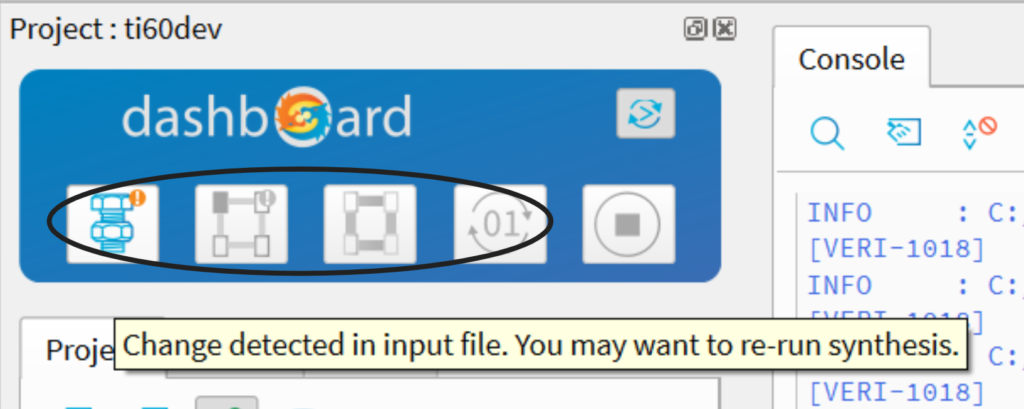

コンパイルする

コンパイルボタンを押して、Bitstream File (.bit / .hex) が生成されるまで待ちます。

Debugger を起動し、信号を観測する

1. Ti60 評価ボードの電源を ON にして、USB-C ケーブルで PC と接続します。

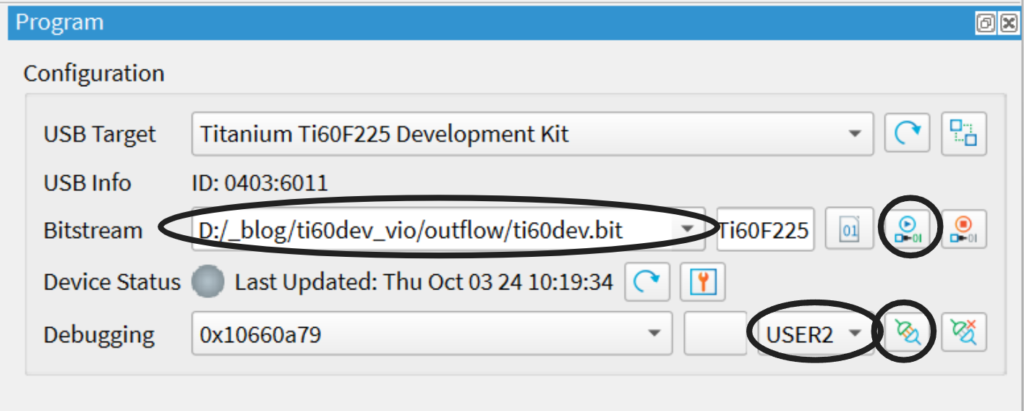

前回同様 Debugger を起動して、Bitstream File を書き込み、JTAG USER2 に接続します。

※ "USER2" は、さきほど Interface Designer で選択した JTAG Resource です。

2. reset の Value を 1 にセットします。

すると、カウンタが動作し始めて led の Value が変化し始めます。

その他 Tips

Debug Core を再編集する

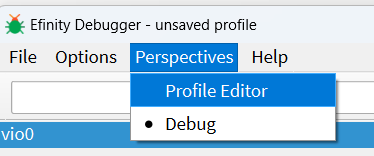

Debug Core を編集するときは、Debugger を起動した後、Perspectives - Profile Editor を選択します。

これで Editor モードと Debug モードを切り替えることができます。

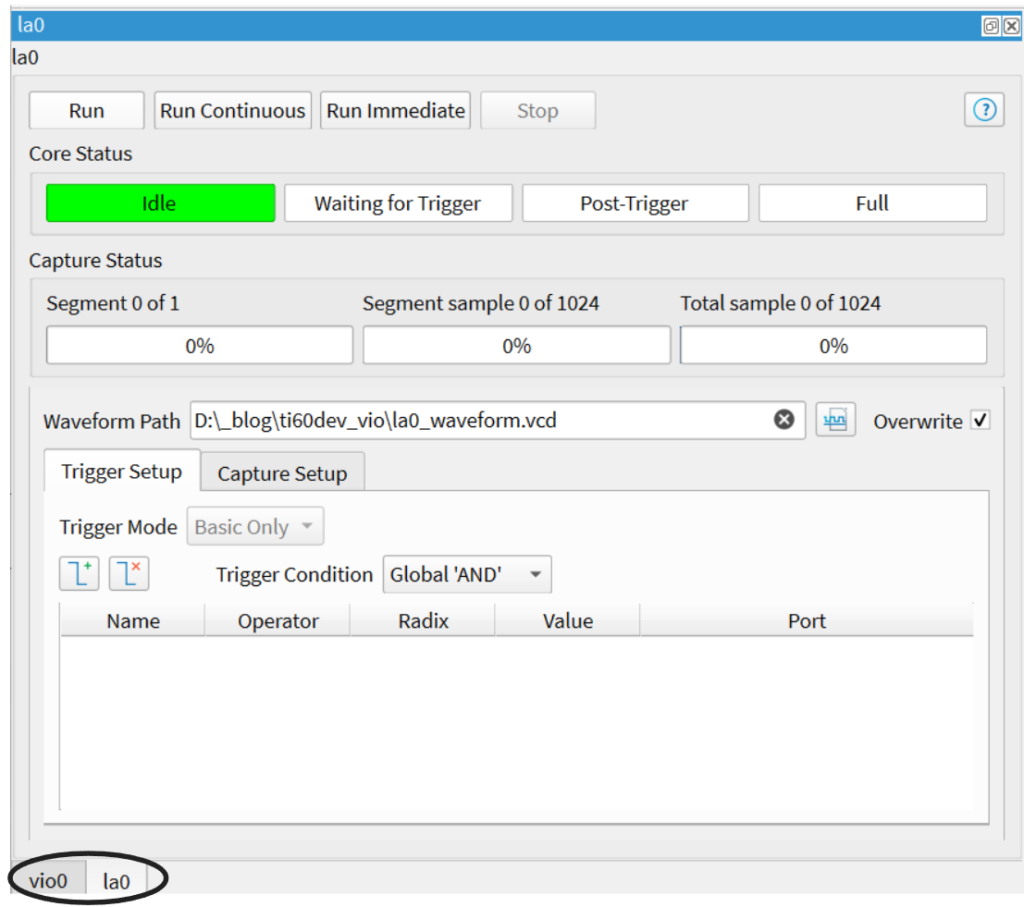

Logic Analyzer を追加する

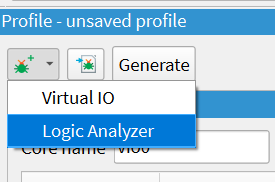

Debug Core に Logic Analyzer を追加することができます。

前回の記事では Logic Analyzer は自動的に挿入されますが、この方法では手動でトップデザインに記述することになります。

Virtual IO と Logic Analyzer は同一の Debug Core に実装され、Debug Core のポート信号が増えます。

信号名とビット幅を入力して Generate を押します。

top.v

module top

(

input CLK,

output [2:0] LED,

: 中略

// Debug Core のインスタンス

// debug_top.v のポートに信号を接続する

//

edb_top edb_top_inst (

.bscan_CAPTURE ( bscan_CAPTURE ),

.bscan_DRCK ( bscan_DRCK ),

.bscan_RESET ( bscan_RESET ),

.bscan_RUNTEST ( bscan_RUNTEST ),

.bscan_SEL ( bscan_SEL ),

.bscan_SHIFT ( bscan_SHIFT ),

.bscan_TCK ( bscan_TCK ),

.bscan_TDI ( bscan_TDI ),

.bscan_TMS ( bscan_TMS ),

.bscan_UPDATE ( bscan_UPDATE ),

.bscan_TDO ( bscan_TDO ),

.vio0_clk ( CLK ),

.vio0_led ( LED ),

.vio0_reset ( nRST ),

// Logic Analyzer の信号が debug_top.v に追加される

.la0_clk (CLK),

.la0_led (LED),

.la0_reset (nRST)

);

endmoduleVirtual IO と Logic Analyzer は Debugger 下部のタブで切り替えることができます。

今回のプロジェクトのダウンロード

ちなみに今回の記事で作成した Design はこちらからダウンロードできますので参考にしてください。

“Efinity Debugger を試す 後編 (Virtual IO 編)” に対して1件のコメントがあります。